# ERX318 for 68000

User's Manual

Zax Corporation

Parenta Billing

17

# ERX318 for 68000 · 68010

User's Guide

Rev. E1.01

### OUTLINE

The ERX318 is an in-circuit emulator for developing and evaluating hardware and software of microprocessor products.

The ERX318 has automated most of the true debugging procedures for development. For example, there is the auto-breakpoint function that sets breakpoints in all instruction steps with symbols by downloading a program; batch and macro functions that enable up to 10 - level nesting; stub function that realizes subroutines substitution and I/O simulation. In addition, the ERX318 has the measurement functions such as performance and coverage analysis for improved product quality.

# ERX318 for \$8000 User's Guide

# CONTENTS

| 1. | SPECIF | ICATION 1                                                   |

|----|--------|-------------------------------------------------------------|

|    | 1.1    | Configuration                                               |

|    | 1.2    | General Specification                                       |

|    | 1.3    | Emulation Function Specification · · · · · 2                |

| 2. | SYSTE  | M CONFIGURATION 5                                           |

|    | 2.1    | ERX318I Configuration · · · · · 6                           |

|    | 2.2    | ERX318P Configuration · · · · · · · · · · · · · · · · · · · |

| 3. | ERX318 | START AND STOP 9                                            |

|    | 3.1    | Turning Power On and Off9                                   |

|    | 3.2    | Start and Stop 10                                           |

| 4. | HANDL  | ING EACH UNIT13                                             |

|    | 4.1    | Interface Connector · · · · · · · · · · · · · · · · · · ·   |

|    | 4.2    | Incircuit connector · · · · · · · · · · · · · · · · · · ·   |

|    | 4.3    | Incircuit Probe                                             |

|    | 4.4    | External Probe                                              |

| 5. | CPU E  | MULATION FUNCTIONS 19                                       |

|    | 5.1    | Probing Target System                                       |

|    | 5.2    | Pin Control 29                                              |

|    | 5.3    | EMSEL Control                                               |

|    | 5.4    | CLOCK 36                                                    |

|    | 5.5    | RESET/HALT:37                                               |

|    | 5.6    | IPL0/IPL1/IPL2                                              |

|    | 5.7    | BERR39                                                      |

|    | 5.8    | BR/BG/BGACK                                                 |

|    | 5.9    | DTACK41                                                     |

|    | 5.10   | VPA/VMA/E42                                                 |

|    | 5.11   | Power Supply and Ground                                     |

| 6  | EMUL/  | ATION MEMORY FUNCTION 45                                    |

|    | 6.1    | Emulation Memory 45                                         |

|    | 6.2    | User Memory                                                 |

|    | 6.3    | Mapping                                                     |

| 7. | REAL - | TIME TRACE FUNCTION 49                                      |

|    | 7.1    | Real - Time Trace Control · · · · · · 50                    |

|    | 7.2    | How to use the Real Time Trace Function · · · · · 52        |

|    |        |                                                             |

| 8. BREAK | FUNCTION 57                                      |

|----------|--------------------------------------------------|

| 8.1      | Monitor Break Function 58                        |

| 8.2      | Event Break Function 58                          |

| 8.3      | Single Step Break Function                       |

| 8.4      | Memory Write Protect Break Function              |

| 8.5      | Memory Garded Access Break Function · · · · · 58 |

| 8.6      | Access Time - Out Break Function 58              |

| 8.7      | Double Bus Fault Break Function59                |

| 8.8      | History Full - Break Function · · · · · 59       |

| 8.9      | Stub Function 59                                 |

| 8.10     | On - Break Function 59                           |

| 9. EVENT | FUNCTION 61                                      |

| 9.1      | Event Points                                     |

| 9.2      | Sequential Function 63                           |

| 9.3      | External Input Output Trigger Function           |

|          | RAGE FUNCTION 65                                 |

| 11 PERF  | DRMANCE FUNCTION 67                              |

# 1. SPECIFICATION

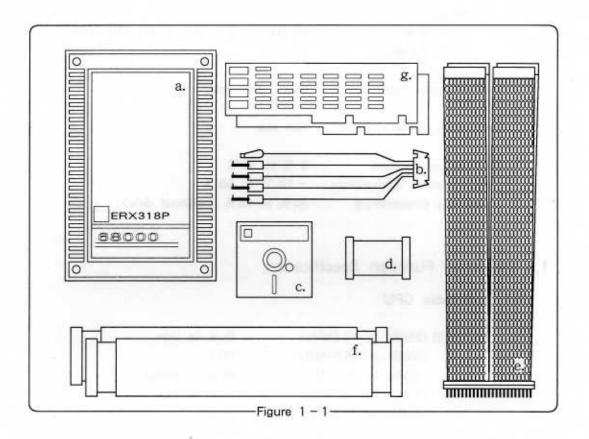

# 1.1 Configuration

#### List of fixtures

a. One ERX Pod

b.One external probe

c. One ERice Diskette

d.One bus cable

e. One in - circuit probe cable

f. Two connecting cables

g.Two internal boards

#### 1.2 General specification

Probe box

Size

85 (H) × 220 (W) × 316 (D) mm

Weight

3.00 Kg

In - circuit probe

500 × 500 mm

External probe

500 mm

Usage temperature

0 °C to 35 °C

Preservation temperature

- 10 °C to 55 °C

Ambient temperature

30% to 85% (without dew)

# 1.3 Emulation Function Specification

#### 1.3.1 Applicable CPU

MC68000 (8MHz to 12.5MHz)

Dual in line

(8MHz to 16.67MHz)

PGA

(8MHz to 16.67MHz)

PLCC (Option)

MC68010 (4MHz to 12.5MHz)

Dual in line

(4MHz to 12.5MHz)

PGA

#### 1.3.2 Emulation memory function

Capacity of emulation memory

256K bytes

Memory space

16M bytes

Emulation memory specification unit

4K bytes

Mapping types

Read - only memory

Read/write memory

User memory

(RW)

(RO)

Nonexistent memory

(US) (NO)

#### 1.3.3 Event Trigger function

Range of address space

Range of data Status types

Pass count range Number of events Sequential specification External trigger specification Up to 64K bytes/64K - byte boundary

Up to 16 bits

Memory read, memory write, memory access,

Inturrupt Acknowledge

16 bits Four blocks Four level (Max)

level trigger | High level

Low level

edge trigger Positive edge

Negative edge

#### 1.3.4 Break function

Break function

Step break function

Map state break functions

Stops in - circuit state

Stops after one instruction is executed

Function that stops emulation when data

is written in the read - only (mapped)

memory area or when the non - existent

memory is accessed.

#### 1.3.5 Real - time trace function

Capacity of trace memory

Trace data widths

Address width Data width

Status width

Auto - start function Auto - stop function Event stop function 8191 - word storage

23 bits 16 bits 7 bits

Starts trace simultaneously when emulation starts Stops trace simultaneously when emulation stops Stops trace if an event occurs

The delay cycle function that sets a trigger in a definite cycle after an event has occurred is also available.

NOTE -

Freeze function

Determines whether trace should be stopped automatically when the trace memory is full or the storage address counter should be rotated Stops trace automatically and generates a break signal when the trace memory is full.

Freeze break function

### 1.3.6 Coverage function

Coverage memory space

64 K bytes × 4 ch/64K - byte boundary

#### 1.3.7 Performance function

Emulation time counter

Measurement time counter

Measurement number counter

Resolution

Error range

Start function

Stop function

48 bits

48 bits × 2ch

1 µs

±5%

Starts measurement if an event occurs

Stops measurement if an event occurs

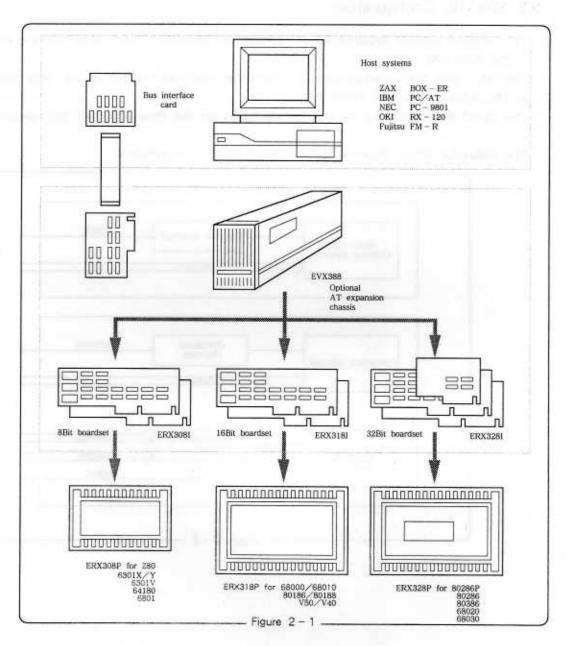

# 2. SYSTEM CONFIGURATION

## 2.1 System Configuration

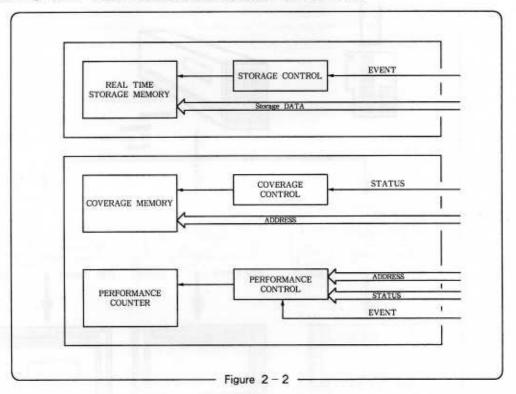

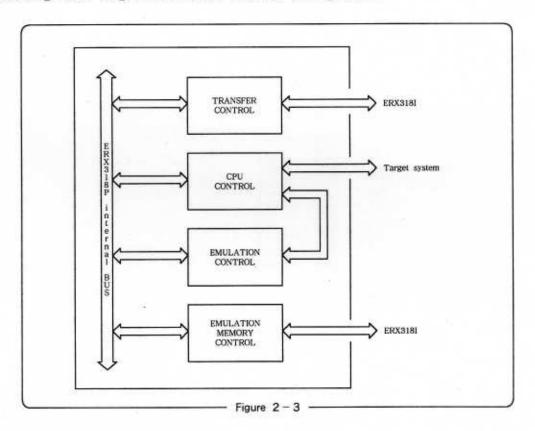

### 2.2 ERX318I Configuration

The common sections required for in - circuit emulation of a 16bit processor are mounted in the ERX318I.

The real-time trace, performance, and coverage functions operate in real time according to the signals from the ERX318P.

The ERX318I is made up of two boards based on the Host extended bus specification.

The following block diagram shows the ERX318I configuration.

# 2.3 ERX318P Configuration

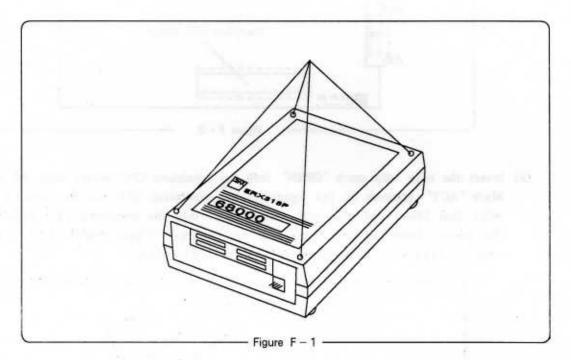

The ERX318P is the unit outside the Host mainframe. The control hardware specific to the target processor is mounted in the ERX318P.

It contains the break sequence control, event control, emulation control, emulation memory control, and memory and I/O access control programs and, the target probe.

The following block diagram shows the ERX318P configuration.

Incircuit Emulator

# 3. ERX318 START AND STOP

#### 3.1 Turning power on and off

#### 3.1.1 Turning power on

When the in-circuit operation is not performed

- ① Turn on the power switch of the host computer.

- ② Start the ERX software.

When the in-circuit operation is performed

- 1 Turn on the power switch of the host computer.

- ② Start the ERX software.

- 3) Turn on the power switch of the target system.

# 3.1.2 Turning power off

If the in-circuit operation has not been performed

- ① Terminate the ERX software.

- ② Turn off the power switch of the host computer.

If the in-circuit operation has been performed

- 1) Turn off the power switch of the target system.

- (2) Terminate the ERX software.

- 3 Turn off the power switch of the host computer.

NOTE -

#### 3.2 Start and stop

#### 3.2.1 File configuration

The basic file configuration contains the following three files:

- a. ERX68K.EXE

- b. ERX68K.HLP

- c. ERX68K.MAC

EXE file

ERX control programs

HLP file

Contains ERX help messages

MAC file

Loads macro when the control program is started.

This occurs only when the file name is the same as the control

program file name.

File name can be changed. If a file is to be renamed, the other basic files must all be renamed. As a result, prompting default characters are changed automatically.

#### 3.2.2 How to start

> program name [batch\_name] < CR >

program\_name

: Specify the name of a file to be started.

batch\_name

: Specify the name of a batch job to be executed after start.

If batch name is omitted, batch processing is not executed.

If a macro file with the same name as program\_name exists, macros are loaded.

| 3.2.3 | How   | to | stop |

|-------|-------|----|------|

| 0.2.0 | 11044 | LU | SLUP |

> Q < CR >

Use the Quit command to stop ERX control software.

The Ctrl + C keys are registered for forceful stop.

| Carlot Carlot Carlo | Emulator |  |

|---------------------|----------|--|

|                     |          |  |

# 4. HANDLING EACH UNIT

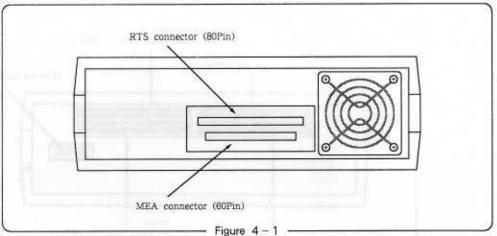

#### 4.1 Interface connector

RTS interface connector

Used for connecting ERX318I and ERX318P. It must be connected to the ERX318I RTS (R-901) port.

MEA interface connector

Used for connecting ERX318I and ERX318P. It must be connected to the ERX318I MEA (R-902) port.

and the state of t

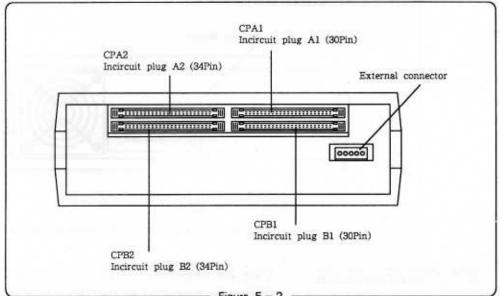

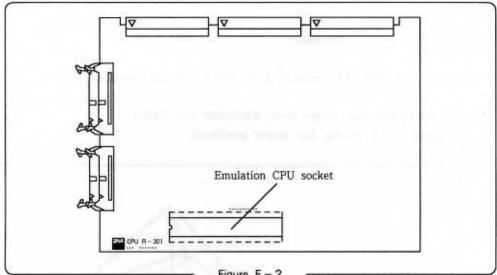

#### 4.2 Incircuit Connector

Figure 5 - 2

| Incircuit connector | Incircuit socket |

|---------------------|------------------|

| CPA1                | CSA1             |

| CPA2                | CSA2             |

| CPB1                | CSB1             |

| CPB2                | CSB2             |

Table 4-1

CAP1 CPA2 CPB1 CPB2

Connectors for connecting the in-circuit probe. Table 4-1 indicates the correspondence between the connectors and incircuit probe outlets. If a target system is not connected, the incircuit probe need not be connected.

External connector

Connector for connecting the external probe

NOTE

Connect the in-circuit probe surely. If connection is abnormal, The ERX may be damaged.

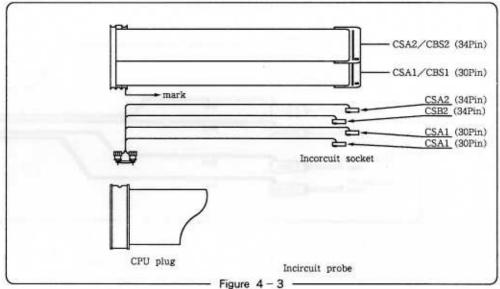

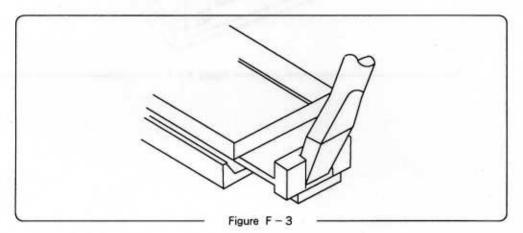

#### 4.3 Incircuit Probe

rigure 4 – 3 ·

| Incircuit connector | Incircuit socket |

|---------------------|------------------|

| CPA1                | CSA1             |

| CPA2                | CSA2             |

| CPB1                | CSB1             |

| CPB2                | CSB2             |

Table 4-2

CSA1 CSA2 CSB1 CSB2

Connector for connecting ERX318P for 68000 mainframe. Table 4-3 indicates the correspondence between the connectors and incircuit probe outlets.

If the target system is not connected, the incircuit probe need not be connected.

NOTE

Connect surely. If connection is abnormal, The ERX may be damaged.

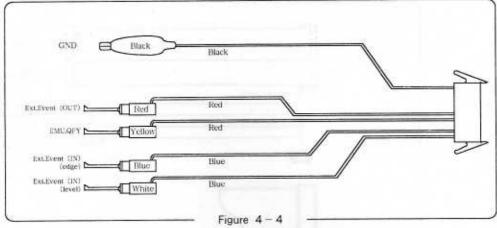

#### 4.4 External Probe

GND

: Ground Ext.Event (OUT) : Event trigger output

EMU.QFY

: Emulation qualification

Ext.Event (IN, edge)

: Event edge trigger input

Ext.Event (IN, level)

: Event level trigger input

Ground

Connect to the ground line of the target system.

Event trigger output

When the event trigger condition is met, a low TTL level signal is output.

This function can be used for output of triggers of instruments such as a logic analyzer and a synchronous

Trigger output can be controlled by the Trigger command.

Emulation qualification

While The ERX is emulating, a high TTL level signal is output. While emulation is stopped, low level signal is output.

Unnecessary signals can be discarded by entering this function in an instrument such as logic analyzer.

#### Event edge trigger input

Event edge trigger can be input in the event function from outside hardware. If event level trigger input is used, this cannot be used.

Input can be controlled by the Event command.

#### Event level trigger input

Event level triggers can be input in the event function from outside hardware.

If event edge trigger input is used, this cannot be used. Input can be controlled by the Event command.

| ircuit Emulator |     |  |      |

|-----------------|-----|--|------|

|                 |     |  |      |

|                 |     |  | - 10 |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 |     |  |      |

|                 | OTE |  |      |

# 5. CPU EMULATION FUNCTIONS

# 5.1 Probing Target System

#### 5.1.1 12.5MHz version

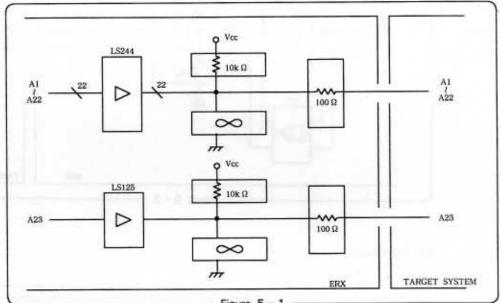

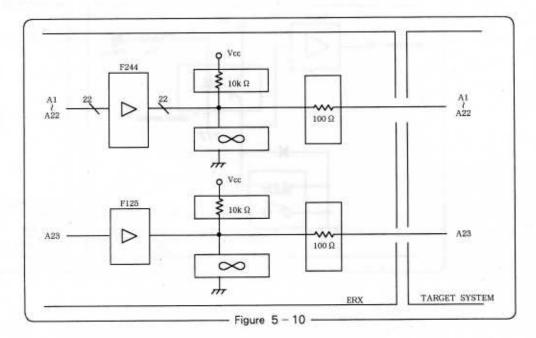

#### (1) Address bus

- Figure 5 - 1 -

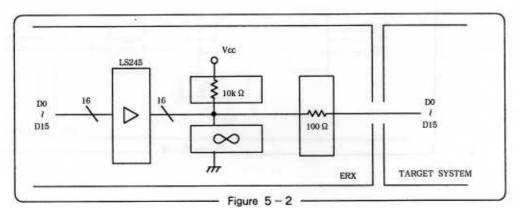

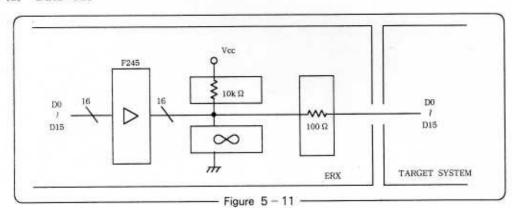

#### (2) Data bus

NOTE

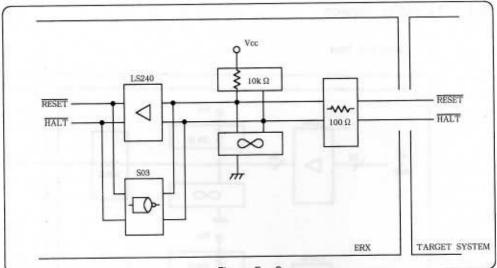

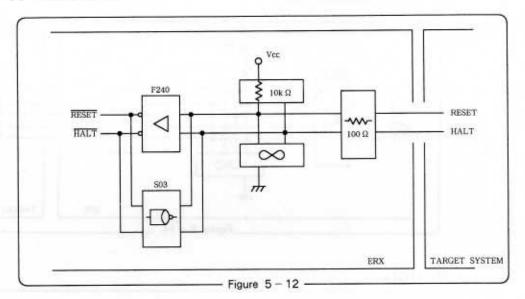

#### (3) RESET, HALT

Figure 5-3

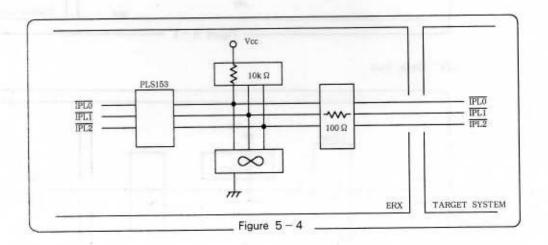

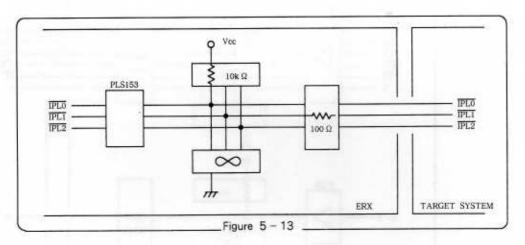

### (4) Interrupt

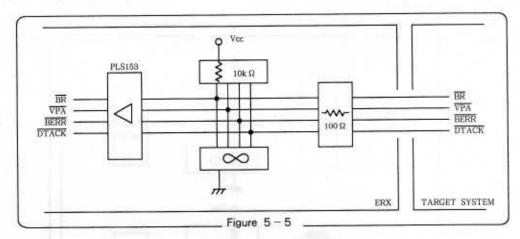

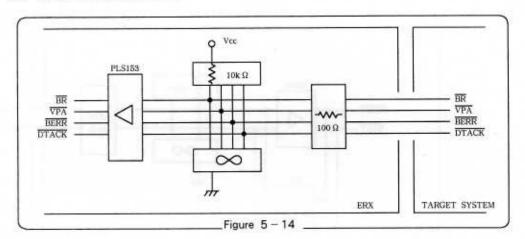

# (5) BR, VPA, BERR, DTACK

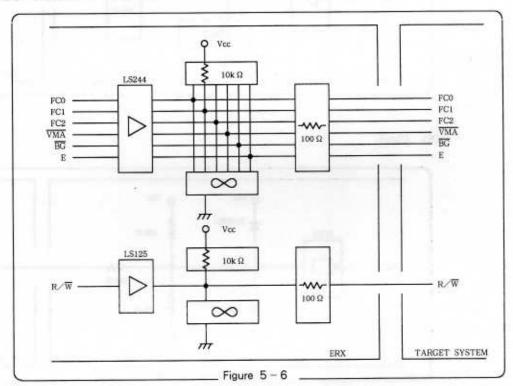

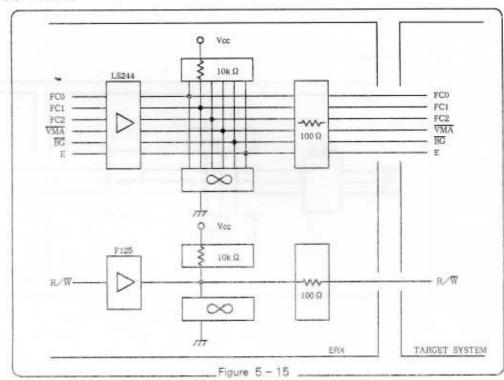

#### (6) Status

NOTE

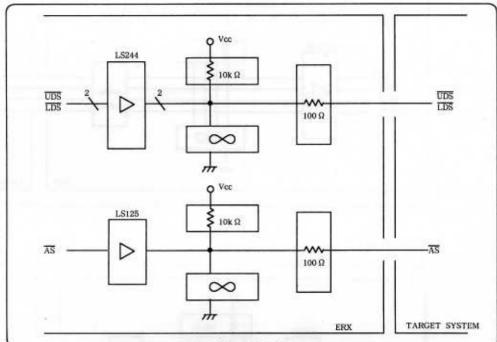

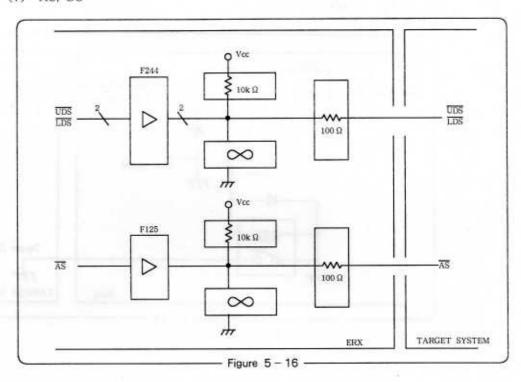

# (7) AS, DS

- Figure 5 - 7

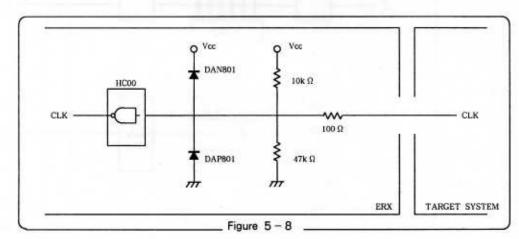

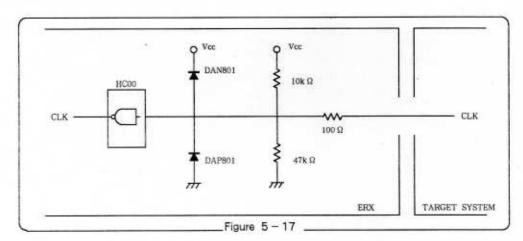

# (8) Clock

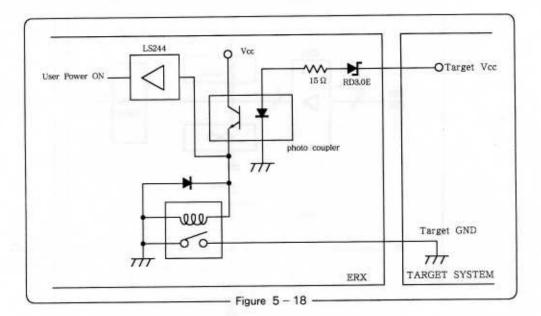

### (9) Power supply

NOTE -

# 5.1.2 16.67MHz version

#### (1) Address bus

(2) Data bus

### (3) RESET, HALT

#### (4) Interrupt

#### (5) BR, VPA, BERR, DTACK

#### (6) Status

# (7) AS, DS

# (8) Clock

NOTE .

### (9) Power supply

# 5.2 Pin Control

|                                      | CONTROL      |      |       |        |        | NWY-SET | TITO C | 2000 | TIM A S | BR    | HALT  | RESET   |       |

|--------------------------------------|--------------|------|-------|--------|--------|---------|--------|------|---------|-------|-------|---------|-------|

| MACHIN CYCLE                         | UDS/LDS AS R | R/¥  | FC0-2 | A1-A23 | D0-D15 | DTACK   | VPA    | BERR | IPL0~2  | BR    | HALI  | KESEI   |       |

| Inerrupt Acknowledge<br>or CPU Space | L            | L    | н     | Н      | OUT    | IN      | AC     | AC   | AC      | N     | AC    | N       | AC    |

| Read                                 | L            | L    | Н     | X      | OUT    | IN      | AC     | AC   | AC      | AC    | AC    | AC      | AC    |

| Write                                | 1.           | L    | L     | X      | OUT    | OUT     | AC     | AC   | AC      | AC    | AC    | AC      | AC    |

| Bus Grant State                      | TS           | TS   | TS    | TS     | TS     | TS      | N      | N    | N       | N     | N     | N       | AC    |

| HALT State                           | н            | Н    | Н     | X      | TS     | TS      | N      | N    | N       | N     | AC    | AC      | AC    |

| RESET State                          | н            | H    | н     | TS     | TS     | TS      | N      | N    | N       | N     | N     | AC      | AC    |

| Emulation<br>Memory Read             | L #1         | L    | н     | х      | OUT    | TS      | N #4   | N    | N #5    | AC    | AC    | AC      | AC    |

| Emulation<br>Memory Write            | H #2         | L    | L     | х      | OUT    | OUT     | N #4   | N    | N #5    | AC    | AC    | AC      | AC    |

| Emulation Break                      | Н            | X #3 | X     | X      | OUT    | TS      | N      | N    | N       | N     | AC    | AC      | N     |

| Pin Command                          | _            | _    | _     | _      | _      | -       | _      | _    | EN/DI   | EN/DI | EN/DI | EN/DI*6 | EN/D) |

Table 5-1

Status : H = High Level

L = Low Level

X = H or L

TS = High Impedance

AC = Accept

N = Not Accept

– = Not Support

- \* 1 If D = Disable is set by the EMSELect command, the LDS/UDS signal is not asserted.

The signal state is H.

- \* 2 If C = Enable is set by the EMSEL®01 command, the LDS/UDS signal is asserted. The signal state is L.

- \*3 If A = Disable is set by the EMSELECT command, the AS signal is not asserted.

The signal state is H.

- \* 4 If G = Enable is set by the EMSELect command, the DTACK signal is accepted. The signal state is AC.

- \* 5 If F = Enable is set by the EMSELset command, the BERR signal is accepted. The signal state is AC.

- \*6 Even if HALT = Disable is set by the Pin command, the HALT signal is accepted when the device is reset.

#### 5.3 EMSEL Control

- (1) EMSEL control functions

- (A) Address strobe (AS) signal control

- (B) Read/write (R/W) signal control

- (C) Data strobe (LDS/UDS) signal control in write cycle

- (D) Data strobe (LDS/UDS) signal control in read cycle

- (E) Data bus signal control

- (F) Bus error (BERR) signal control

- (G) User wait (DTACK) signal control

- (H) Double bus fault break control

- (I) Auto wait signal control

- (J) Time out break signal control

- (K) Control of wait time of the auto wait signal

- (L) Control of clock count of the time out break signal

- (2) Control of the user wait (DTACK) and auto wait signals

#### 5.3.1 EMSEL control functions

(A) Address strobe (AS) signal control

When emulation is broken, output of the address strobe (AS) signal to the target system can be controlled.

(1) Enable

When emulation is broken, the AS signal is asserted to the target system in a repetitive pattern of idle loop command fetch of the emulation CPU. In emulation, the AS signal is asserted in an access cycle of either the emulation memory (RO/RW mapping is set) or user memory (US mapping is set).

(This is the default at initialization.)

(2) Disable

When emulation is broken, the AS signal is not asserted to the target system (high level).

In emulation, the AS signal is asserted in an access cycle of either the emulation memory or user memory.

- (B) Read/write (R/W) signal control When emulation is broken, output of the read/write (R/W) signal to the target system can be controlled.

- (1) Enable

When emulation is broken, the R/W signal is asserted to the target system in a repetitive pattern of idle loop command fetch of the emulation CPU. In emulation, the R/W signal is asserted in an access cycle of either the emulation memory (RO/RW mapping is set) or user memory (US mapping is set). (This is the default at initialization.)

(2) Disable

When emulation is broken, the R/W signal is not asserted to the target system (high level).

In emulation, the R/W signal is asserted in an access cycle of either the emulation memory or user memory.

- (C) Data strobe (LDS/UDS) signal control in write cycle In a write cycle of the emulation memory, output of the LDS/ UDS signal to the target system can be controlled.

- (1) Enable In a write cycle of the emulation memory (RO/RW mapping is set), the LDS/UDS signal is asserted to the target system.

- (2) Disable In a write cycle of the emulation memory (RO/RW mapping is set), the LDS/UDS signal is not asserted to the target system (high level). (This is the default at initialization.)

- (D) Data strobe (LDS/UDS) signal control in read cycle In a read cycle of the emulation memory, output of the data strobe (LDS and UDS) signals to the target system can be controlled.

- (1) Enable In a read cycle of the emulation memory (RO/RW mapping is set), the LDS/UDS signal is asserted to the target system.

- (2) Disable In a read cycle of the emulation memory (RO/RW mapping is set), the LDS/UDS signal is not asserted to the target system (high level).

(E) Data bus signal control

In a read cycle of the emulation memory, output of the data bus (D0 to D15) signals to the target system can be controlled.

(1) Enable

In a read cycle of the emulation memory, data of the emulation memory is output to the data buses D0 to D15.

(2) Disable

In a read cycle of the emulation memory (RO/RW mapping is set), the data buses D0 to D15 are in high impedance.

(This is the default at initialization.)

\*In a write cycle to emulation memory, the data bus D0 to D15 are always in high impedance.

(F) Bus error (BERR) signal control

When the emulation memory is accessed, the bus error (BERR) signal of the target system can be validated.

(1) Enable

The BERR signal of the target system is validated in an access cycle of either the user or emulation memory and BERR processing is emulated, and bus error processing is emulated.

(2) Disable

The BERR signal of the target system is validated in an access cycle of the user memory (US mapping is set) only.

The BERR signal is ignored in an access cycle of the emulation memory (RO/RW mapping is set).

(This is the default at initialization.)

(G) User wait (DTACK) signal control

When the emulation memory is accessed, the wait (DTACK) signal of the target system can be validated.

(1) Enable

The DTACK signal of the target system is validated in an access cycle of either the user or emulation memory and BERR processing is emulated. In emulation, the access cycle is terminated by the DTACK or VPA signal of the target system.

#### (2) Disable

The DTACK signal of the target system is validated in an access cycle of the user memory (US mapping is set) only.

The DTACK signal is ignored in an access cycle of the emulation memory (RO/RW mapping is set) and emulation starts without wait state. (This is the default at initialization.)

#### (H) Double bus fault break signal control

If the processor enters double bus fault state in emulation, the break signal can be generated.

#### (1) Enable

If the processor enters double bus fault state in emulation, the double bus fault break signal is generated and monitor control is restored automatically. (This is the default at initialization.)

#### (2) Disable

The processor stops in double bus fault state.

Initialize the processor by resetting the target system.

Monitor control can be restored by the STOp command.

#### (I) Auto wait signal control

The auto wait signal inputs the wait signal generated by the ERX wait signal generator in the DTACK pin of the processor.

#### (1) Enable

In emulation, a two-clock (or one to seven clock) pulse wait state is inserted in each machine cycle. In an access cycle of the user memory (US mapping is set) in this situation, a two clock pulse wait state is generated inside ERX even if the DTACK signal answers in S4 state. After the two-clock pulse wait state, if the DTACK signal of the target system is acknowledged, the machine cycle is terminated.

At this time, one to seven-clock pulse wait state times can be selected by the EMSEL control function (K).

#### (2) Disable

In emulation, a wait state is not generated inside ERX.

Ordinary real time emulation is performed.

(This is the default at initialization.)

(J) Time - out break control

If memory access is executed in emulation state and the DTACK or VPA signal is not answered within 32K clock pulses (the clock value can be changed), the break signal can be generated. If memory access is executed in monitor state, a time – out error can also be generated.

At this time, a clock count value can be selected from 8 to 32K clock pulses by the EMSEL control function (L).

(1) Enable

If a time - out is detected, the break signal and a time - out error are generated.

that the tent to be the tent to the tent t

(This is the default at initialization.)

(2) Disable

Time - out detection is not performed.

If the DTACK or VPA signal is not answered in emulation, monitor control can be restored by the STOp command.

If memory access is executed in monitor state, control can be returned by the ESC key.

- (K) Control of wait time of the auto wait signal Auto wait time of the auto wait signal can be selected from among one to seven clock pulses.

- (1) One clock pulse wait

- (2) Two clock pulse wait (default at initialization)

- (3) Three clock pulse wait

- (4) Four clock pulse wait

- (5) Five clock pulse wait

- (6) Six clock pulse wait

- (7) Seven clock pulse wait

- (L) Control of clock count of the time out break signal The clock count value of the time - out break signal can be selected from among 8 to 32K clock pulses.

- (1) 8 clock pulses

- (2) 128 clock pulses

- (3) 2K (2048) clock pulses

- (4) 4K (4096) clock pulses

- (5) 8K (8192) clock pulses

- (6) 16K (16,384) clock pulses

- (7) 32K (32,768) clock pulses (default at initialization)

### 5.3.2 Control of use of the user wait (DTACK) and auto wait signals

| Auto wait | User wait<br>(DTACK) | Auto wait             | > User wait * 1            | Auto wait < User wait * 2 |                            |  |

|-----------|----------------------|-----------------------|----------------------------|---------------------------|----------------------------|--|

| EMSEL (I) | EMSEL (G)            | User<br>memory access | Emulation<br>memory access | User<br>memory access     | Emulation<br>memory access |  |

| Disable   | Disable              | User's DTACK          | Non Wait                   | User's DTACK              | Non Wait                   |  |

| Disable   | Enable               | User's DTACK          | User's DTACK               | User's DTACK              | User's DTACK               |  |

| Enable    | Disable              | Auto Wait             | Auto Wait                  | User's DTACK              | Auto Wait                  |  |

| Enable    | Enable               | Auto Wait             | Auto Wait                  | User's DTACK              | User's DTACK               |  |

Table 5-2

- \*1 If auto wait time is longer than user wait (DTACK) time

- \*2 If auto wait time is shorter than user wait (DTACK) time

NOTE -

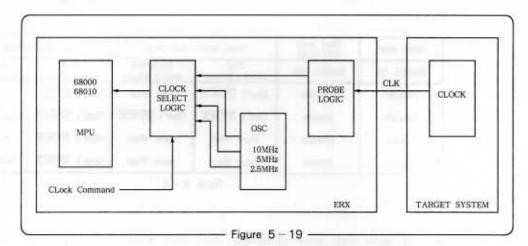

#### 5.4 Clocks

The clock source can be selected from among the following options by using the Clock command:

- (0) External clock (TTL level: max 20MHz) The target system clock is used. Use this clock when debugging clock - synchronized circuits.

- (1) Internal clock (10MHz)

- (2) Internal clock ( 5MHz)

- (3) Internal clock (2.5MHz)

This clock is generated inside the ERX.

(If the internal clock is used, the target system will not receive the clock signal.)

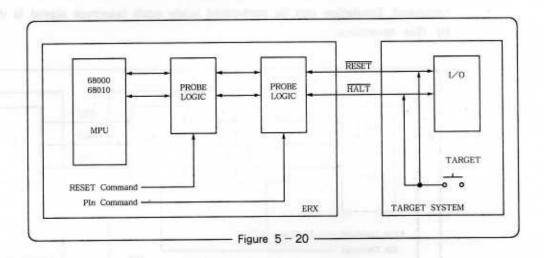

## 5.5 RESET/HALT

While the emulation MPU is emulating the target system, if the RESET/HALT signal is asserted by resetting the target system manually, a hardware reset is caused in the emulation MPU.

This is the same as an ordinary MPU.

While the emulation MPU is breaking emulation, a hardware reset is not caused in the emulation MPU by resetting the target system manually.

The emulation MPU register must be reset by the Register RESet command.

The RESet command resets the emulation MPU and the ICERESet command resets the entire ERX.

The  $\overline{\text{RESET}}/\overline{\text{HALT}}$  signal from the target system is enabled/disabled by the **Pin** command. Thus, emulation can be performed with the  $\overline{\text{RESET}}/\overline{\text{HALT}}$  signal line disconnected.

NOTE -

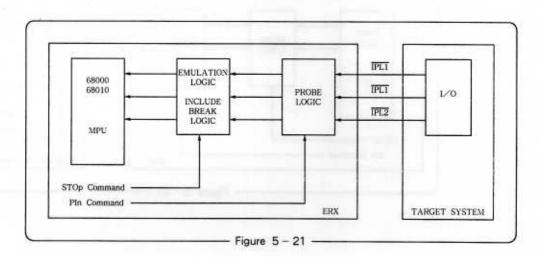

## 5.6 IPLO/IPL1/IPL2

The ERX generates a level-7 interrupt in the emulation MPU when using the STOp command. This interrupt has priority over the level-7 interrupt of the target system.

Like the STOp command, an emulation break that is set by the Break command also generates a level-7 interrupt. When the emulation MPU is in emulation break state, the level-7 interrupt signal of the target system is masked.

However, even when the emulation MPU is in emulation break state, level-7 F.F of the emulation MPU is set by the level-7 edge trigger. So, a level-7 interrupt generated during emulation break generates an interrupt sequence when execution is changed from monitoring to target emulation.

The level-1 to 6 interrupt signals are masked when the emulation MPU is in emulation break state.

The level-1 to 7 target interrupt signals can be controlled by using the Pin command. Emulation can be performed while each interrupt signal is disconnected by this operation.

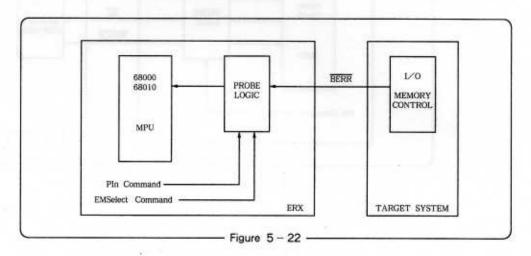

#### 5.7 BERR

The BERR signal is accepted in the machine cycle when the user memory (US mapping setting) is accessed. At this time, bus error handling by combining the BERR and HALT signals can also be emulated.

Ordinarily, the BERR signal is ignored in the machine cycle when the emulation memory (RO, RW mapping setting) is accessed.

However, the BERR signal can be accepted by using the EMSELect command irregardless of map setting state.

The BERR signal from the target system can be controlled by using the Pin command. Emulation can be performed while the BERR signal is disconnected by this operation.

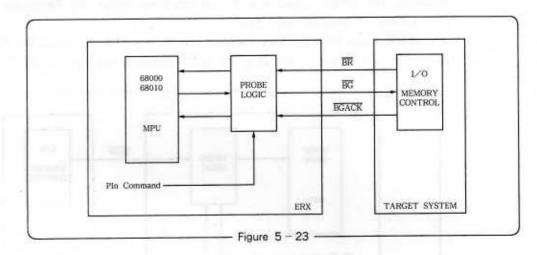

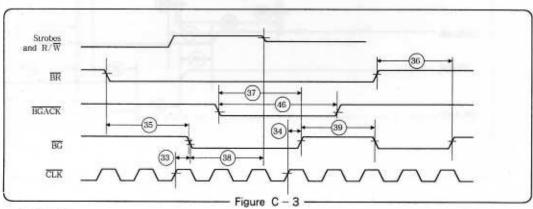

## 5.8 BR/BG/BGACK

The  $\overline{BR}$  and  $\overline{BGACK}$  signals are accepted at any time.

Therefore, even if an emulation break occurs while the target system is operating the DMA by the  $\overline{BR}$  signal, the DMA can still operate properly.

The  $\overline{BR}$  signal from the target system can be controlled by using the Pin command. Emulation can be performed while the  $\overline{BR}$  signal is disconnected by this operation.

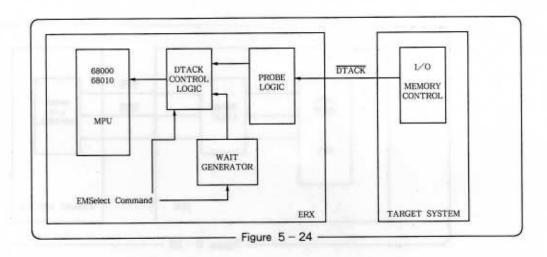

## 5.9 DTACK

When G = enable is set by the EMSELect command, the  $\overline{DTACK}$  signal is accepted in each machine cycle.

When G = enable is set, the  $\overline{DTACK}$  signal is delayed and a 2-byte clock (or 1 to 7-byte clock) wait state can be generated in each machine cycle in the ERX.

NOTE .

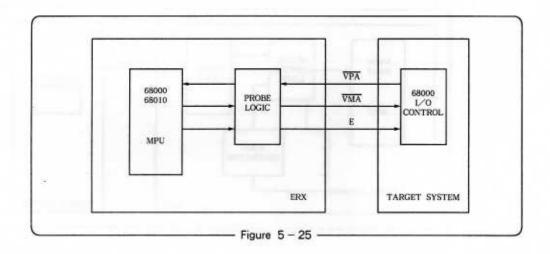

## 5.10 VPA/VMA/E

In a machine cycle in which the user memory or I/O device (US mapping is set) is in access, the  $\overline{VPA}$  signal is accepted. In a machine cycle in which the emulation memory (RO/RW mapping is set) is in access, the  $\overline{VPA}$  signal is ignored. The  $\overline{VMA}$  signal, which is an answer to the  $\overline{VPA}$  signal, does the same function as an ordinary MPU.

The E clock signal is always outputting clock pulses to the target system.

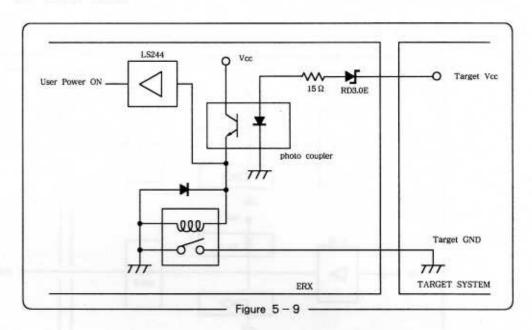

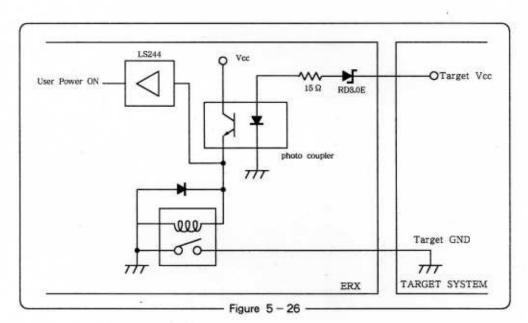

#### 5.11 Power Supply and Ground

The ERX is continuously monitoring the target system power supply.

When the probe is connected normally and the target system power is turned on, the target system and ERX GND are connected by a relay.

If the probe is inserted reversed or the target system power is turned off, the relay is turned off and target system and ERX GND are disconnected. This function avoids destruction of the probe buffers and target system due to improper connection of the probe.

Incircuit Emulator

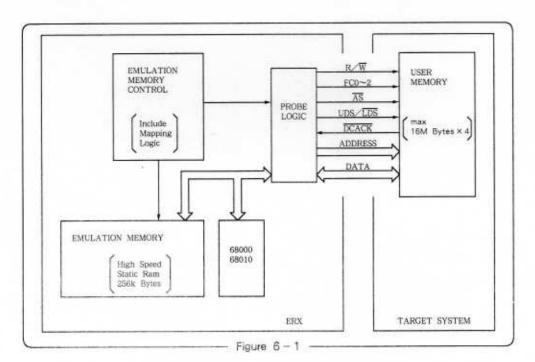

## 6. EMULATION MEMORY FUNCTION

## 6.1 Emulation Memory

The ERX has built - in 256K-bytes of high-speed static RAM as emulator memory for target programs. It is called emulation memory as compared to a user memory (target system memory).

This emulation memory can substitute for any memory in the 4G-byte memory area. This can be accomplished by allocating a 64K-byte emulation memory block to any memory location in the 4G-byte memory area by using the MAp command. The emulation memory is made up of a high-speed static RAM and can meet all low-speed to high-speed systems requirements.

When a target system views the emulation memory, the memory looks different from ordinary memory because it is built in the ERX probe.

The ERX address, data, and control bus pins must be in high impedance when buses are grounded. Because of the emulation characteristics, DMA transfer between target system and emulation memories is disabled but DMA transfer between the target system memory space and emulation memory is not a problem.

#### 6.2 User Memory

The ERX can assign a 4G-byte memory space to a user memory in 64K-byte memory space units.

The timing when the ERX writes in the target system memory is equal to the processor access timing. The timing when the ERX reads from the target system memory is a little shorter than the processor access timing. For details, see the AC charcteristics in Appendix.

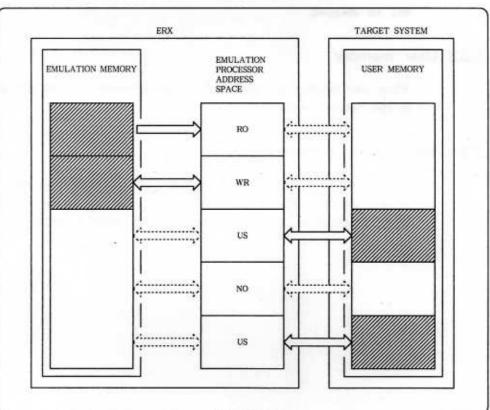

## 6.3 Mapping

The ERX selects one from among four kinds of memories in 64K - byte units. The following figure shows a block diagram.

- (1) Read/write memory (RW)

- (2) Read only memory (RO)

- (3) User memory

- (4) Nonexistence memory(NO)

The four kinds of memories are explained below.

Figure 6 – 2 –

47

### 6.3.1 Read/Write memory

If a read/write memory is specified, the target processor uses the emulation memory in the ERX as an accessable memory space instead of the RAM memory of the target system.

### 6.3.2 Read-only memory

When a read - only memory is specified, the target processor uses the emulation memory in the ERX as an accessable memory space, instead of the ROM device of the target system. The target processor cannot rewrite the memory space defined as a read - only memory. When this area of memory is written to, emulation will be stopped.

#### 6.3.3 User memory

When user memory is specified, the target processor accesses the memory mounted in the target system.

## 6.3.4 Nonexistent memory

When nonexistent memory is specified, it means that no memory is mounted in the specified memory space. So, if the target processor accesses the memory space specified as nonexistent memory, emulation is stopped.

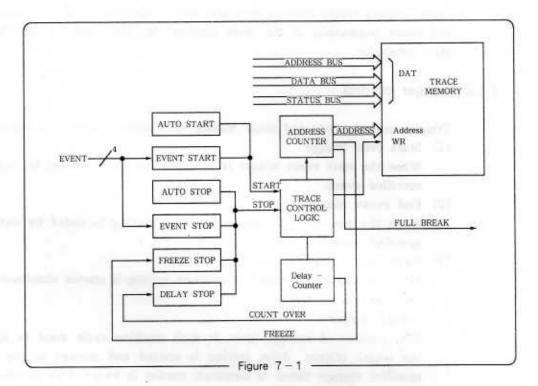

## 7. REALTIME TRACE FUNCTION

The function that traces the execution contents in real time during emulation is called the real time trace function.

The real time trace function consists of two control functions such as the trace and trigger control functions.

The trace control function traces the execution contents in each machine cycle during emulation.

## 7.1 Real Time Trace Control

#### 7.1.1 Trace control

Trace control traces address, data, and status information in each machine cycle and stores sequentially in the trace memory. So, trace contents can be confirmed after emulation.

### 7.1.2 Trigger control

Trigger control starts and stops tracing. Each control function is explained below.

- (1) Start even trigger When the start event trigger is specified, tracing is started by output of the specified event.

- (2) End event trigger When the end event trigger is specified, tracing is ended by output of the specified event.

- (3) Auto start trigger When the auto start trigger is specified, tracing is started simultaneously when emulation is started.

- (4) Length trigger

The number of storage times in each machine cycle must be specified in

the length trigger. After tracing is started and storage to the number of

specified storage times is executed, tracing is ended. This function is valid

only when the start event trigger is specified.

- (5) Multi-trigger

When the multi-trigger is specified, tracing is started each time the start event trigger is generated. If this function is omitted, tracing is started by the first start event trigger generated after emulation and the second and subsequent start event triggers are ignored.

(6) Freeze trigger

When the freeze trigger is specified, storage is stopped when the trace memory is full after tracing is started. If this function is omitted, the trace memory overflows after tracing is started. The trace memory, however, rotates and updates old contents.

### 7.1.3 History full break control

Full break control generates the full break signal when the trace memory is full. So, when the trace memory is full in emulation, emulation can be broken.

## 7.2 How to Use The Real Time Trace Function

The real time trace function is realized by each trigger control function explained in Section 5.1. Varieties of trace modes can be created by combining these trigger control functions.

Some basic modes needed for incircuit emulation are distributed in the standard macro library. For details on how to handle the standard macro library, see Appendix A.

This Section describes the eight modes provided in standard macro library.

| (1) End monitor mode    | (EM) |

|-------------------------|------|

| (2) Begin monitor mode  | (BM) |

| (3) End event mode      | (EE) |

| (4) Begin event mode    | (BE) |

| (5) Center event mode   | (CE) |

| (6) Multiple event mode | (ME) |

| (7) Inner event mode    | (IE) |

| (8) Outer even mode     | (OE) |

Table 7-1 lists the parameters of the History command for realizing these eight modes,

|                | Start Event | End Event | Auto Start | Length | Multi | Freese |

|----------------|-------------|-----------|------------|--------|-------|--------|

| End Monitor    | OFF         | OFF       | ON         | OFF    | OFF   | OFF    |

| Begin Monitor  | OFF         | OFF       | ON         | OFF    | OFF   | ON     |

| Begin Event    | *           | OFF       | OFF        | *      | OFF   | ON     |

| Center Event   | *           | OFF       | ON         | 2047   | OFF   | OFF    |

| End Event      | OFF         | *         | ON         | OFF    | OFF   | OFF    |

| Multiple Event | *           | OFF       | OFF        | *      | ON    | *      |

| Inner Event    | *           | *         | *          | OFF    | OFF   | *      |

| Outor Event    | *           | *         | *          | OFF    | OFF   | *      |

Table 7-1

<sup>\*</sup> The specified value can be changed.

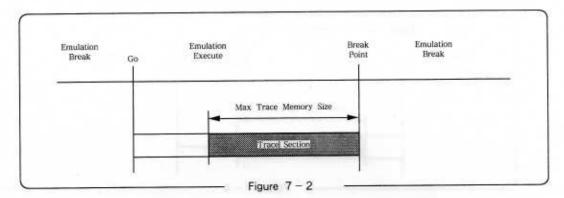

#### 7.2.1 End monitor mode

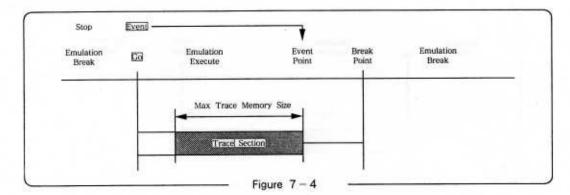

When emulation is started by the command, The trace buffer is started. At a breakpoint or when an emulation break is generated by the STOp command, the trace is stopped. The trace range ends with the cycle immediately before an emulation break is generated.

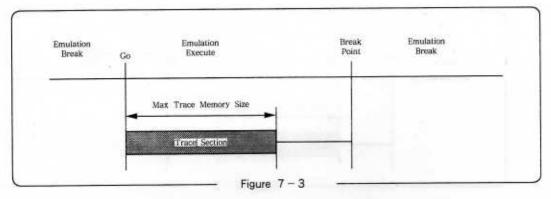

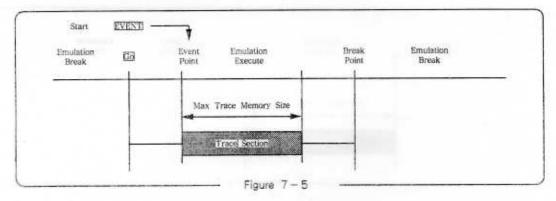

#### 7.2.2 Begin monitor mode

When emulation is started by the Go command, trace is started. When the max trace memory size is traced, the trace is stopped automatically.

The trace range begins immediately after emulation is started by the Go command and does not exceed the maximum trace memory cycle.

### 7.2.3 End event mode

When emulation is started by the Go command, trace is started.

When the specified event point is passed, the trace is stopped automatically.

The trace range ends with the cycle immediately before the event point is passed and does not exceed the max trace memory cycle.

#### 7.2.4 Begin event mode

When the event point specifying start of emulation by the 60 command is passed, trace is started. When the maximum trace memory size is stored, the trace is stopped automatically. The trace range begins immediately after the specified event point is passed and does not exceed the max trace memory cycle.

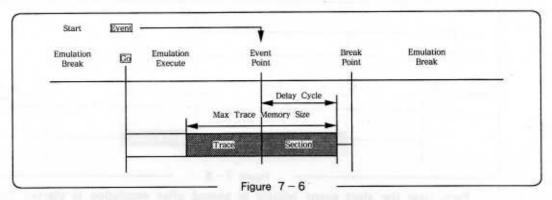

#### 7.2.5 Center event mode

When emulation is started by the Go command, trace is started. When the max trace memory size is traced, the trace is stopped automatically.

The trace range begins immediately after the specified event point is passed and does not exceed the maximum trace memory cycle.

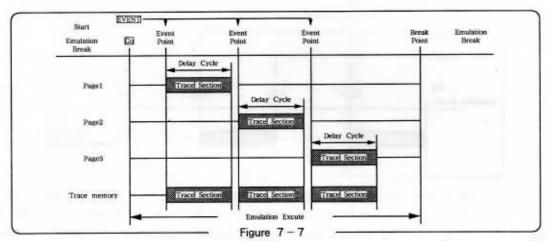

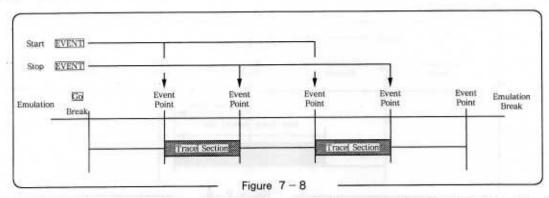

#### 7.2.6 Multiple event mode

When traceing is performed by using the same event point more than once, multiple event mode is used. Each time the event point is passed after emulation is started by the Go command, trace is started. The tracing range begins immediately after the event point is passed and does not exceed the delay cycle.

#### 7.2.7 Inner event mode

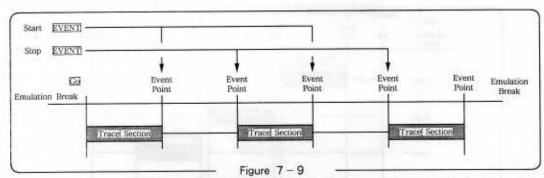

Each time the start event pointer is passed after emulation is started by the Go command, tracing is started. Each time the stop event pointer is passed, the tracing buffer is stopped. The operation range of the emulation processor seen by the real – time trace can be limited by using this mode. The mode is useful when attention is concentrated on a specific program module and program operation is to be analyzed.

#### 7.2.8 Outer event mode

Each time the start event point is passed after emulation is started by the Go command, tracing is stopped. Each time the stop eventpoint is passed, traceing is started. The function of this mode is the opposite of the function of the inner event mode. The operation range of the emulation processor that need not be seen by real – time trace can be excluded by the outer event mode.

When the interrupt processing module is excluded and application module program operation is to be analyzed, this mode is also useful.

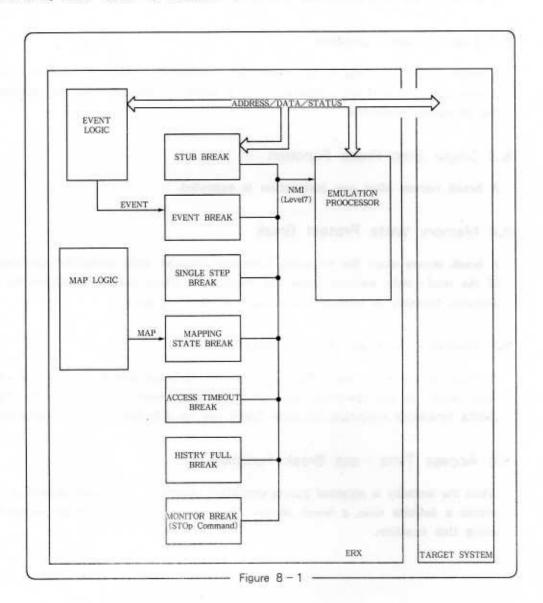

## 8. BREAK FUNCTION

The function that forces the processor to stop during emulation is called the break function. A break occurs when one of the following eight conditions is met. The break function is controlled by NMI (level 7) signal.

#### 8.1 Monitor Break Function

A break occurs unconditionally according to the operator specification.

#### 8.2 Event Break Function

A break occurs according to the eventpoint specification, when the machine cycle condition is met by the hardware comparator. So, a break is generated in the machine cycle of the emulation processor.

## 8.3 Single Step Break Function

A break occurs after one instruction is executed.

### 8.4 Memory Write Protect Break

A break occurs when the emulation processor executes write access for the specified space of the read - only memory using the mapping function during emulation execution. The accessed memory is protected, and may not be written to.

## 8.5 Memory Guarded Access Break Function

A break occurs when the emulation processor executes access (read, write, or operation code fetch) to the specified space of nonexistent memory using the mapping function during emulation execution. Program errors can be detected easily by using this function.

#### 9.6 Access Time - out Break Function

When the memory is accessed during emulation execution, if acknowledgment is not received within a definite time, a break ocuurs. Memory access errors can be detected easily by using this function.

#### 8.7 Double Bus Fault Break Function

When the processor enocounters a double bus fault during emulation, a break occurs and control returns to the monitor.

When the power is turned off, the processor in double bus fault state is stopped.

The processor can be initialized when it is reset by the target system.

Control can be returned to the monitor by using the STOp command,

### 8.8 History Full - Break Function

A break occurs when in the trace memory becomes full during emulation execution.

#### 8.9 Stub Function

A break occurs when an instruction specifying a software break point is fetched.

This is a before - execution break because the instruction at the break point is not executed and emulation is halted.

Actually, the break function is initiated by an exception generated when an illegal instruction is executed, and control returns to the monitor.

The software break function can be specified only for accessible (read/write) memory when an illegal instruction must be inserted in the program.

When the function is specified for the read - only memory, data is transferred from the read - only memory of the target system to the emulation memory and after that the software break function is enabled using emulation memory (read - only memory).

#### 8.10 On - break Function

The program operation can be changed freely by intervening software.

Software can be intervened by combining operation commands.

Actually, emulation is interrupted by a hardware break generated by the event function and the specified command, macro, or batch job is executed.

So, the on - break function is not a debug function in real - time mode.

NOTE -

Incircuit Emulator

NOTE -

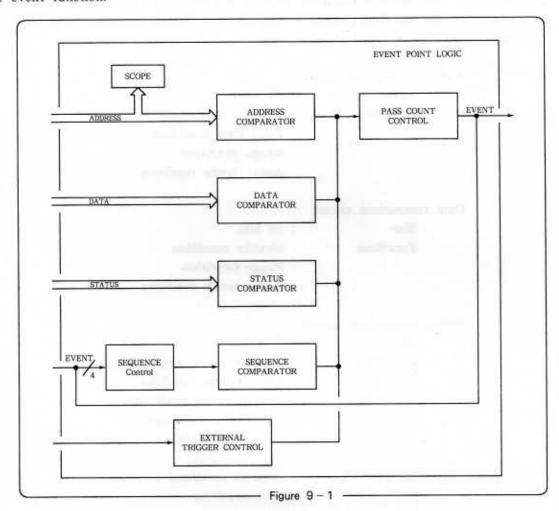

# 9. EVENT FUNCTION

The function that supplies a trigger signal to each of the ERX emulation execution, analysis, and measurement functions in real time by using the machine cycle comparator is called the event function.

## 9.1 Event Points

The circuit that monitors emulation state in real time and that outputs an event trigger signal when the specified conditions (address, data, status, bus count sequential, external trigger) are met is called an event point.

Address comparison circuit

Size

: 23 bits

Functions

: Identity condition

Don't Care condition Range condition

Auto - break condition

Data comparison circuit

Size

: 16 bits

Functions

: Identity condition

Range condition

Auto - break condition

Status comparison circuit

Size

: 6 bit

Functions

: Memory access condition

Memory read condition Memory write condition Interrupt acknowlidge Supervisor condition

User condition Program condition Data condition

Passcount function

Size

: 16 bit

#### 9.2 Sequential Function

The function that specifies the sequence of the specified event points in more than two channels is called the sequential function. This function cannot control branch. Therefore, sequential function can be specified in serial mode.

#### 9.3 External Input Trigger Function

The function that inputs an asynchronous signal as a condition from an event point is called the external input trigger function. The external signal that has been input is synchronize with the address, data, and status condition in the event point circuit. An external input trigger signal can be selected from among the following four types:

(1) Level signal: High level active

(2) Level signal : Low level active

(3) Pulse signal : Positive edge

(4) Pulse signal : Negative edge

Actually, an asynchronous signal is input from the external probe. For details, see Section 4.4

#### 9.4 External Output Trigger Function

This function outputs the identity signal from the event point to the outside. Actually, an asynchronous signal is input from the external probe. For details, see Section 4.4

#### 9.5 Scope Function

The function that monitors in real time the target processor program counter location while executing program memory during emulation is called the scope function.

NOTE -

| and the second section of the sectio |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

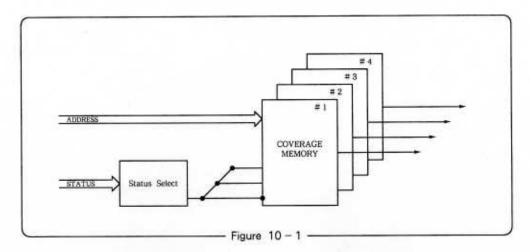

## 10. COVERAGE FUNCTION

The function that measures in real time the target program test and that represents the program reliability in numeric is called the coverage function.

Actually, when a certain address of the emulation processor is accessed, the function that sets the coverage memory outputs a test result. So, before the coverage function is used, coverage memories must be allocated to the memory spaces to be measured and the coverage memories must be all accessed. After that, when emulation is started, the executed programs and accessed memories are plotted in the coverage memories. When emulation is broken, the distribution of the programs and memory accessed during emulation can be measured. Each measured value is displayed in percentage.

| Incircuit Er |  |

|--------------|--|

NOTE -

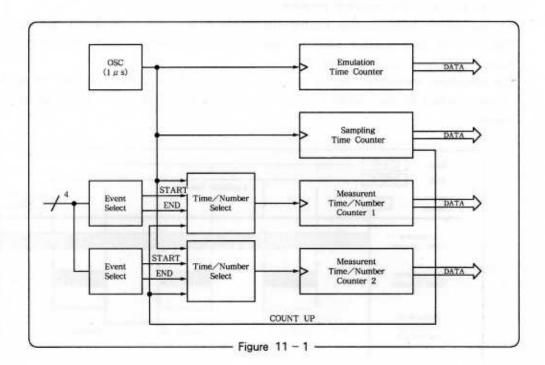

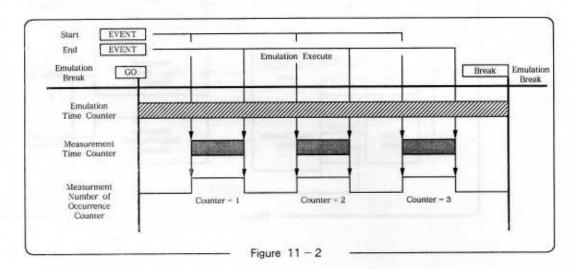

# 11. PERFORMANCE FUNCTION

The function that measures execution time between two event points, or that measures the number of execution times at one event point, is called the performance function.

NOTE -

The performance function is made up of an emulation time counter, a measure time counter, and a measurement number counter.

The emulation time counter counts the  $1-\mu$ s basic clock to measure the execution time. The measurement number counter measures the number of event points that have been passed between the start and end events.

The emulation execution time is the total execution time in the specified range, the number of event points in the specified range, and processor load ratio are displayed as measurement results.

GIB SEE STATE

APPENDIX

17

# ERX318 for 68000 • 68010

## **APPENDIX**

Rev. E1.01

## ERX318 for 68000 - 68010 APPENDIX

## CONTENTS

| A. STAI | NDARD MACRO LIBRARY   |                                 |

|---------|-----------------------|---------------------------------|

| A.1     |                       |                                 |

| A.2     |                       |                                 |

|         | MH                    |                                 |

|         | DIR                   |                                 |

|         | TYPE                  |                                 |

|         | MEDIT                 | Control Control Control Control |

|         | SETUP                 |                                 |

|         | EM                    | ç                               |

|         | BM                    |                                 |

|         | BE                    |                                 |

|         | CE                    | 100                             |

|         | EE                    | 13                              |

|         | ME                    |                                 |

|         | IE                    |                                 |

|         | OE                    |                                 |

|         | AIE                   | 17                              |

|         | AOE                   | 18                              |

| B. HLLD | D MACRO LIBRARY       |                                 |

| B.1     | 1 Outline             | 19                              |

| B.2     | 2 Configlation ······ | 19                              |

| B.3     | 3 System flow         | 20                              |

| B.4     | 4 Function            | 21                              |

| B.5     | 5 Operation ······    | 22                              |

| B.6     | 6 Command function    | 24                              |

|         | HLLD                  | 25                              |

|         | MH                    | 26                              |

|         | BL                    | 27                              |

|         | NBL                   | 28                              |

|         | T                     |                                 |

|         | BX                    | 30                              |

|         | DX                    |                                 |

|         | DS                    |                                 |

|         | DL                    |                                 |

|         | H/V                   |                                 |

|         | Veiw                  |                                 |

|         | V-i                   | 20                              |

|    |       | Veiw    | 37                                    |

|----|-------|---------|---------------------------------------|

|    |       |         | 38                                    |

|    | 1.00  |         | 39                                    |

|    |       | Veiw    | 40                                    |

|    |       | Veiw    | 41                                    |

|    |       | Veiw    | 42                                    |

|    |       | Veiw    | 43                                    |

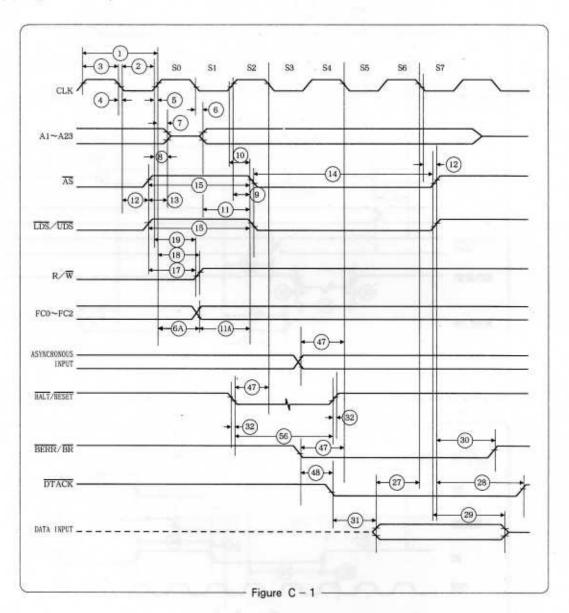

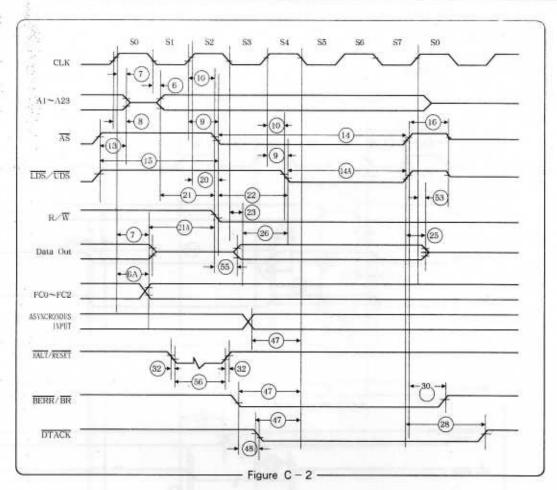

| C. | AC CH | ARAC    | TERISTICS                             |

|    | C.1 S | ignal ' | Timing43                              |

| D. | EMULA |         | CPU INLET                             |

|    | D.1   | Attac   | hing/Detaching Emulation CPU ······47 |

| G  | CVT68 | v       | 51                                    |

# A. STANDARD MACRO LIBRARY

## A.1 Outline

The standard macro library is a macro file provided by Zax Corporation.

When the ERX is started, the standard macro library is loaded automatically.

The macro commands, can be executed using the ERX commands by using this library named.

File name: ERX68K.MAC

The configuration and procedure of the standard macro library are the same as those of a user - created macro file.

The standard macro library loads the macros when the ERX is started. The user macro file loads the macros when the MLoad command is executed.

# MH

### Function

The MH command displays the command help messages of the standard macro library.

Input format

> MH < CR >

> MH SETUP < CR >

Input example

ERX>MH

Help message

:

:

## DIR

Function

The DIR command displays a list of files on the disk.

Input format

> DIR [path\_name] < CR >

path\_name

: Directory path name. Specify the file name.

Input example

ERX>dir \*. bat

Volume in drive C has no label Directory of C: ≺USER≺

SAMPLE BAT 174 10.10.86 12:00p DEMO BAT 2648 12.10.86 12:00p 2 File(s) 2685418 bytes free

ERX>

NOTE

The MS-DOS wild card can be assigned to the file name.

## TYPE

## Function

The TYPE command displays a text file to the screen.

Input format

> TYPE File\_name < CR >

file\_name : Text file name

Input example

ERX> type sample.doc This is a sample document

ERX>

NOTE

TYPE

## MEDIT

## Function

The MEDIT command modifies the emulation or target memory using the screen editor.

## Input format

> MEDIT beg\_addr,end\_addr < CR >

beg\_addr

: Specify the modification begin memory address.

end\_addr

: Specify the modification end memory address.

## Input example

ERX>MEDIT 1000, 13FF

: Screen editor

ERX>

## SETUP

## Function

The SETUP command initializes the following when emulation is started:

- 1. Clock selection

- 2. Memory mapping

- 3. Pin control

- 4. Object program downloading

- 5. Other setup command settings

The **SETUP** command has two functions. One function specifies the initial condition in an interactive format. The other function initializes the emulator with specified conditions.

When initial conditions are specified in interactive format, a file (CONFIG.CNF) is created automatically.

This file can be used for automatic initialization.

### Input format

> SETUP < CR > Setup by CONFIG.CNF File (Yes or < cr > /No) = N < CR >Select Clock  $(0-3) = \operatorname{clock\_mode} < CR >$ Memory Start Address or < CR > = start\_address < CR > Memory End Address = end\_address < CR > Mapping Type (RW/RO/NO/US) = map\_type < CR > Pin Control (Di/En) = DI EN < CR > Load Object File object\_file\_name < CR > Key in command ro < CR > = command < CR > > SETUP < CR > Setup by CONFIG.CNF File (Yes or < CR > /No) = Y < CR >...... auto set

Setup by CONFIG.CNF: Specifies initialization.

Y Initializes by using the CONFIG.CNF file.

N Initializes by key input.

by this setting, the initial conditions are stored

in the CONFIG.CNF file.

clock\_mode : Selects a target CPU clock.

0 | 1 | 2 | 3

start\_address : Specifies the mapping starting address.

If only < CR > is entered, control is moved from mapping

specification to the next specification.

end\_address : Specifies the mapping end address.

map\_type : Specifies the mapping type.

RO | RW | US | NO

pin\_control : Controls the mask of the target CPU signal.

DI | EN

object\_file\_name : Specifies the object file to be downloaded.

command : Specifies other initialization commands.

7

## Input example

ERX>setup

Setup by CONFIG. CNF File (Yes or <CR> / No) = n

==== Clock Setup ====

0 External Clock (TTL)

1 Internal Clock (10MHz)

2 Internal Clock (5MHz)

3 Internal Clock (2.5MHz)

Select Clock (0-3) = 2

NOTE -

```

==== Map Setup ====

Memory Start Address or <CR>

= 1000

= OFFFF

Memory End Address

Mapping Type (RW/RO/NO/US)

= us

= 0

Memory Start Address or <CR>

Memory End Address

= Offf

Mapping Type (RW/RO/NO/US)

Memory Start Address or <CR>

==== Pin Setup ====

Pin Control (Di/En) = di

==== Object Setup ====

Load Object File Name = sample.abs

ERX>setup

Setup by CONFIG. CNF File (Yes or <cr> / No) = y

==== Clock Setup ====

Internal Clock (4MHz)

==== Map Setup ====

map

0000 - OFFF = RO

1000 - FFFF = US

==== Pin Setup ====

Pin

RESET* = High (Diaable)

NMI *

= High (Disable)

= High (Disable)

IWT#

BUSRO* = High (Disable)

WAIT*

= High (Disable)

=== Object Setup ====

Load Object File Name = sample.abs

ERX>

```

NOTE

SETUP

| 100 | 1 /1  |

|-----|-------|

|     | 11/21 |

|     | 100   |

Function

The EM command sets history trigger mode as end monitor mode.

Input format

Input example

ERX>EM

ERX>

| F-37 | 1 1/17 |

|------|--------|

| 1011 | 1 //// |

| - TI | VII    |

|      | 111    |

Function

The BM command sets history trigger mode as begin monitor mode.

Input format

> BM < CR >

Input example

ERX>BM ERX>

## BE

Function

The BE command sets history trigger mode as begin event mode.

Input format

> BE event\_symbol < CR >

event\_symbol : Specify the defined event symbol name.

Input example

ERX>BE MAIN. LOOP1 ERX>

## CE

Function

The GE command sets history trigger mode as center event mode.

Input format

> CE event\_symbol < CR >

event\_symbol : Specify the defined event symbol name.

Input example

ERX>CE MAIN. LOOP1 ERX>

Function

The EE command sets history trigger mode as end event mode.

Input format

> EE event\_symbol < CR >

event\_symbol : Specify the defined event symbol name.

Input example

ERX>EE MAIN. LOOP1 ERX>

## ME

Function

The ME function sets history trigger mode as multiple event mode.

Input format

> ME event\_symbol,length < CR >

event\_symbol : Specify the defined event symbol name.

length

: Specify the amount of one - time storage.

input example

ERX>ME MAIN, LOOP1, 20

ERX>

## Œ

## Function

The IE command sets history trigger mode as inner event mode.

## Input format

> IE start\_event, end\_event < CR >

start\_event

: Specify the symbol name of the event that becomes the trace

start trigger.

end\_event

: Specify the symbol name of the event that becomes the trace

end trigger.

## Input example

ERX>IE MAIN. START, MAIN. END

ERX>

NOTE -

## OE

## Function

The OE command sets history trigger mode as outer event mode.

## Input format

> OE start\_event, end\_event < CR >

start\_event

: Specify the symbol name of the event that becomes the trace

interrupt trigger.

end\_event

: Specify the symbol name of the event that becomes the trace

restart trigger.

## Input example

ERX>OE SUB. START, SUB. RETURN ERX>

## AIE

### Function

The AIE command adds inner event mode triggers.

## Input format

start\_event, end\_event < CR > > AIE

start\_event : Specify the symbol name of the event that becomes the

trace start trigger.

end\_event

: Specify the symbol name of the event that becomes the trace

end trigger.

## Input example

ERX>AIE SUB1. START, SUB1, RETURN

## AOE

## Function

The AOE adds outer event mode triggers.

## Input format

> AOE start\_event, end\_event < CR >

start\_event

: Specify the symbol name of the event that becomes the

trace interrupt trigger.

end\_event

: Specify the symbol name of the event that becomes the trace

and board board board board board board board board board

restart trigger.

## Input example

ERX>AOE SUB2. START, SUB2. RETURN ERX>

# B. HLLD MACRO LIBRARY

## B.1 General Description

The ERX for 68000 high - level language debugger is a real time high - level language debugger realized in ERX on the basis of the symbols and objects output by the user generated source program and compiler.

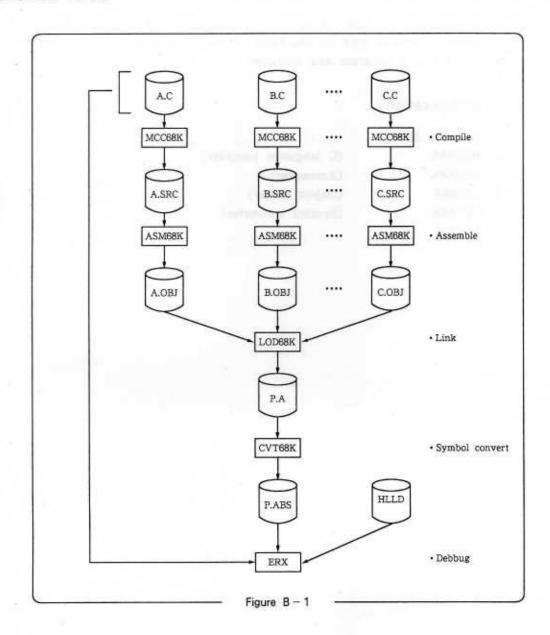

## **B.2** Configuration

- (1) ERX for 68000

- (2) MCC68K

(C language compiler)

- (3) ASM68K

- (Assembler)

- (4) LOD68K

- (Object loader)

- (5) CVT68K

- (Symbol converter)

## B.3 SYSTEM FLOW

## B.4 Explanation of Functions

The ERX high level language debugger has the following functions in addition to the ERX functions.

### B.4.1 Command help

The command help function displays the high level language debugging command syntax.

### B.4.2 Break point line setting

The breakpoint line setting function sets a break point in a desired source line number.

### B.4.3 Break point line release

The break point line release function releases the break point set in the source line number.

### B.4.4 Source line step execution

The source line step execution function executes the specified lines of the source program.

## B.4.5 Break source line display

The break source line display function displays the source of the line that caused emulation break.

### B.4.6 Break source line dump display

The break source line dump display function displays dump of the memory corresponding to the line that caused emulation break.

## B.4.7 Character string variable display

The character - string variable display function displays character - string variables by the NULL code or up to 128 bytes by the ASCII code.

#### B.4.8 Local area dump display

The local area dump display function displays dump of the local area used by the current functions.

### B.4.9 Stack frame display

The stack frame display function displays function names and arguments from the current position to route function.

### B.4.10 History source display

The history source display function displays the history contents by the source line.

## B.4.11 Source program display

The source program display function displays the specified source program.

## B.5 Explanation of Operations

## B.5.1 Compiler and assembler option specification

The compiler and assembler options of the source file (s) to be debugged must be specified as follows:

>MCC68K (file\_name) /debug=lines;

>ASM68K (file\_name) /d/case;

>LOD68K (file\_name) :

For details, see the MCC68K User's Guide and ASM68K User's Guide.

### B.5.2 Program execution setup

#### B.5.2.1 Start ERX68K and prepare for debugging.

- (1) Mapping (MAp command)

- (2) Register reset (R RES command)

- (3) Program loading (Load command)

- (4) High level language debug macro loading (HLLD command)

- (5) Register reset (R RES command)

- (6) Source file directory specification (View command)

Execution setup is needed each time ERX is started. This operation can be done easily by using the SETUP command (see the standard macro library).

### **B.6 Command Functions**

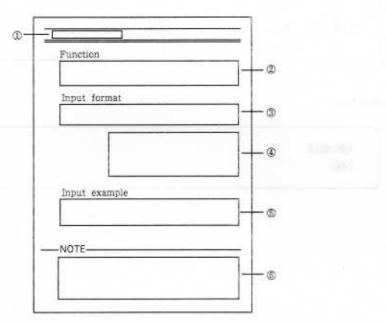

This section explains the commands in alphabetical order. The commands are explained in the following format.

## B.6.1 Command explanation format

① Command name : Name of the command to be input.

Uppercase characters cannot be omitted.

(Lowercase characters can be omitted.)

2 Function : Command function

3 Input format : How to activate the command

The command is indicated in abbreviation.

A lowercase character string indicates a parameter.

4 Input parameters: Lowercase characters in the input format.

Required parameters are explained.

⑤ Input example : Actual input example

⑥ NOTE : Note (s) on use

# HLLD

## Function

The **HLLD** command defines a command for debugging varieties of high level languages.

## Input format

> HLLD < CR >

## Input example

ERX>HLLD ERX>

# MH

## Function

The MH command displays the command syntax of the high level language debugger.

## Input format

> MH HLLD < CR >

HLLD

: Specify the high-level language debugger.

## Input example

ERX>MH HLLD

Help messages

ERX>

BL

Function

The BL command sets a break - point in the desired source line number.

Input format

> BL source\_line < CR >

source\_line : Specify the source program line number.

Input example

ERX>BL 52 ERX>BL \*

## NBL

## Function

The NBL command releases the break - point set in the source line number.

## Input format

> NBL source\_line < CR >

source\_line : Specify the source program line number.

27

## Input example

ERX>NBL 52 ERX>NBL \*

7

### Function

The T command executes the specified lines of the source program.

Input format

>T [step] < CR >

step

Specify the number of source steps to be executed in a decimal number.

The default is one.

Input example

ERX>T ERX>T 10

|             | 00 |

|-------------|----|

|             | W  |

| $ D\rangle$ | 1  |

Function

The BX command displays the source of the line that caused emulation break.

Input format

> BX < CR >

Input example

ERX>BX

Break source line

ERX>

## Function

The DX command displays dump of the memory corresponding to the line that caused emulation break.

## Input format

> DX [Length] < CR >

Length

: Specify the display byte count in a hexadecimal number. If this parameter is omitted, dump up to the next symbol address is displayed.

## Input example

ERX>DX ERX>DX 100

The DS command displays a character - string variable by NULL ('  $\searrow$ 0') code or up to 128 bytes by ASCII characters.

### Input format

> DS address < CR >

> DS event\_symbol < CR >

address

: Specify the display start address in a hexadecimal number.

event\_symbol

: Specify the display start symbol.

#### Input example

>DS 1000

>DS MAIN. MESSAGE

NOTE -

| 150 | -  | . 10 |

|-----|----|------|

| 11  | 3  | 1//  |

|     | 11 | w    |

| 11  | 11 | 11   |

The DL command displays dump of the local area used by the current functions.

Input format

> DL < CR >

Input example

ERX>DL

The H/V displays the history file contents by the source lines.

# Input format

> H/V [beg\_point] [,end\_point] < CR >

beg\_point

: Specify the search start point in a decimal number from 1

to 8191.