# AICA (FQ8005) Sound-block User's Manual Ver. 1.00

#### **Contents**

# **Overview of AICA**

# **Pin Table**

# **Block Diagram**

Sound block

# **Register Map**

Channel data

Common data

DSP data

# **Overview of Registers**

| <u>Channel data</u> | Common data         | <b>DSP data</b>      |

|---------------------|---------------------|----------------------|

| -KYONEX             | -MONO               | - <u>COEF[12:0]</u>  |

| - <u>KYONB</u>      | -MVOL[3:0]          | -MADRS[16:1]         |

| - <u>SSCTL</u>      | - <u>DAC18B</u>     | -MPRO                |

| - <u>LPCTL</u>      | -MEM8MB             | - <u>TEMP[23:0]</u>  |

| - <u>PCMS</u>       | - <u>VER[3:0]</u>   | - <u>MEMS[23:0]</u>  |

| - <u>SA[22:0]</u>   | - <u>RBL[1:0]</u>   | -MIXS[19:0]          |

| -LSA[15:0]          | -RBP[22:11]         | - <u>EFREG[15:0]</u> |

| - <u>LEA[15:0]</u>  | -MOFUL              | - <u>EXTS[15:0]</u>  |

| - <u>D2R[4:0]</u>   | -MOEMP              | -                    |

| - <u>D1R[4:0]</u>   | -MIOVF              | -                    |

| - <u>AR[4:0]</u>    | -MIFUL              | -                    |

| - <u>LPSLNK</u>     | - <u>MIBUF[7:0]</u> | -                    |

| - <u>KRS[3:0]</u>   | - <u>MOBUF[7:0]</u> | -                    |

| - <u>DL[4:0]</u>    | - <u>MSLC[5:0]</u>  | -                    |

| - <u>RR[4:0]</u>    | - <u>AFSEL</u>      | -                    |

| - <u>OCT[3:0]</u>   | - <u>CA[15:0]</u>   | -                    |

| - <u>FNS[9:0]</u>   | - <u>LP</u>         | -                    |

| - <u>LFORE</u>      | - <u>SGC[1:0]</u>   | -                    |

|                     |                     |                      |

-LFOF[4:0] -EG[12:0] -<u>PLFOWS[1:0]</u> -<u>MRWINH[3:0]</u> --<u>PLFOS[2:0]</u> -DMEA[22:1] -ALFOWS[1:0] -DRGA[14:1] -ALFOS[2:0] -DGATE -TL[7:0] -DDIR -<u>ISEL[3:0]</u> -DEXE -DLG[14:1] -IMXL[3:0] -DISDL[3:0] -TACTL[2:0] -DIPAN[4:0] -<u>TIMA[7:0]</u> -Q[4:0]-<u>TBCTL[2:0]</u> -FLV0[12:0] -TIMB[7:0] -FLV1[12:0] -TCCTL[2:0] -TIMC[7:0] -FLV2[12:0] -FLV3[12:0] -SCIEB[10:0] -FLV4[12:0] -SCIPD[10:0] -<u>FAR[4:0]</u> -SCIRE[10:0] -FD1R[4:0] -SCILV0[7:0] -FD2R[4:0] -SCILV1[7:0] -FRR[4:0] -SCILV2[7:0] -EFSDL[3:0] -MCIEB[10:0] -EFPAN[4:0] -MCIPD[10:0] -MCIRE[10:0] -ARMRST -RP -L[7:0]-M[7:0]-RTC[31:0]

# **Overview of Technology**

Loop control

**ADPCM**

**AEG**

PG

LFO

**MIXER**

**FEG**

**DSP**

# **Electrical Specifications**

Absolute Maximum Ratings

Recommended Operating Conditions

Electrical Characteristics under Recommended Operating Conditions

# **History of Updates**

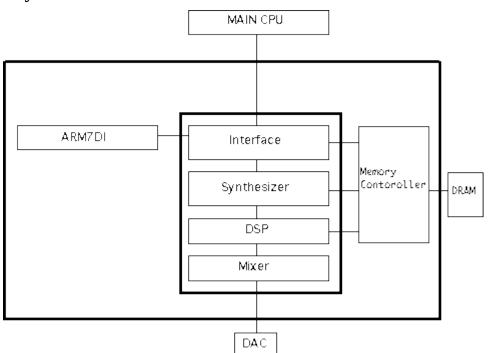

### **Overview of AICA**

### Internal CPU (ARM7).

• Readied with seven prioritized interrupt flags (registers).

#### **PCM Sound block.**

- The PCM data is 16- or 8-bit linear format.

- The ADPCM data is 4-bit yamaha original format.

- Independent LFO mounted in separate slots.

- 64-ch, four-segment EG.

- Forward loop function.

- Generation of up to 64 sounds.

- LPF for time transition of cutoff frequency through four-segment EG.

- ADPCM also capable of pitch change (1 octave maximum).

### 128-step DSP

• DSP that tuned up SCSP.

### **Digital mixer**

By connecting external 16M bit SDRAM, the CPU, sound block, DSP and G2 i/F block can be used together.

Supports RTC(real time clock) back up\_able by externally adding battery.

**Contents**

# Pin Table

| Signal Name | Pin | Function Overview                   |           |

|-------------|-----|-------------------------------------|-----------|

| CK33        | 1   | Master clock (33 MHz)               |           |

| FLC         | 1   | Filter capacity for PLL             |           |

| VDDP        | 1   | Power source for PLL                |           |

| VSSP        | 1   | GND for PLL                         |           |

| VRTC        | 1   | Power source for RTC                |           |

| RTCK        | 2   | RTC clock (32 k)                    |           |

| RESETN      | 1   | Reset signal                        | 3.3 V TTL |

| INTN        | 1   | External interrupt request input    | 3.3V TTL  |

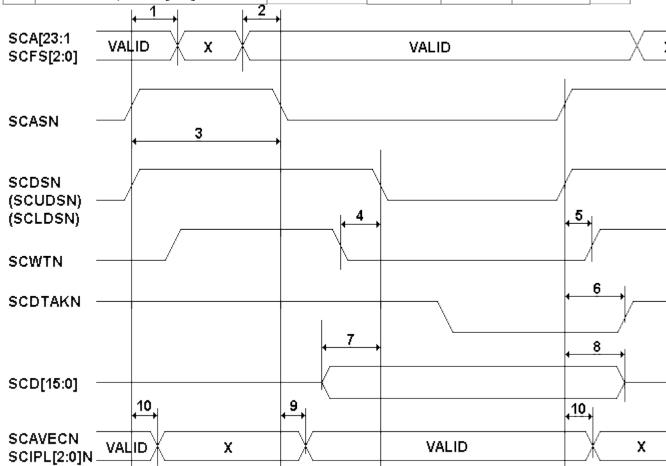

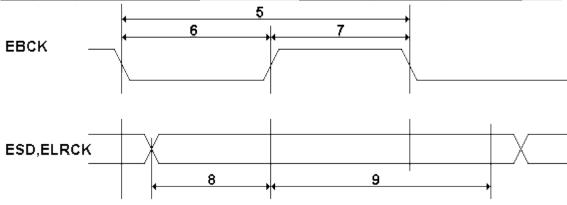

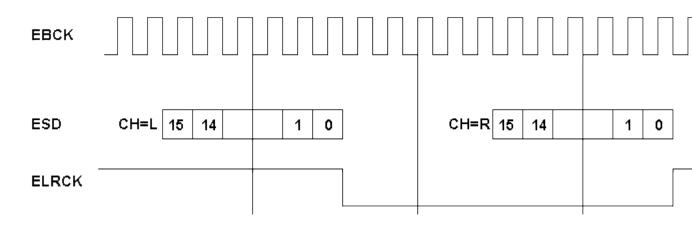

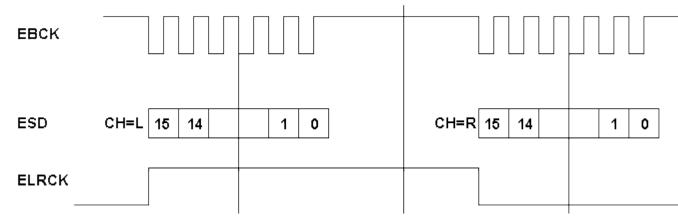

| ESD         | 1   | DIGITAL AUDIO I/F serial data input | 3.3V TTL  |

| EBCK        | 1   | DIGITAL AUDIO I/F BCK               | 3.3V TTL  |

| ELRCK       | 1   | DIGITAL AUDIO I/F LRCK              | 3.3V TTL  |

| MIDIIN      | 1   | MIDI input                          | 3.3V TTL  |

| MIDIOUT     | 1   | MIDI output                         | 3.3V TTL  |

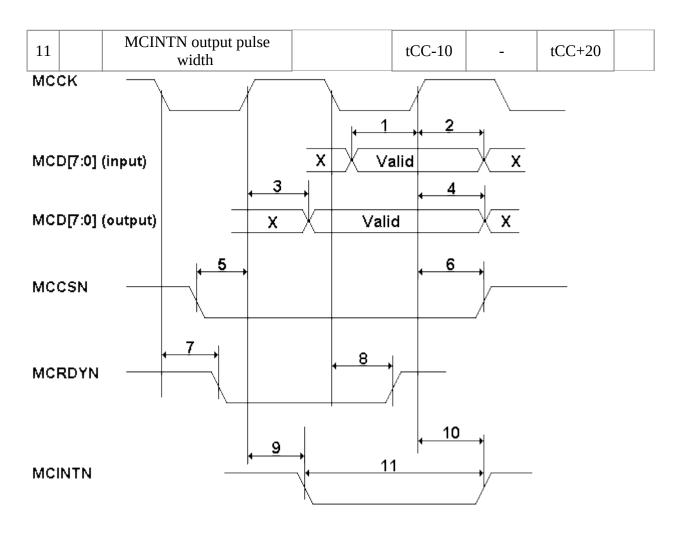

| MCCK        | 1   | G1 bus clock (98.4 M/4)             | 3.3V TTL  |

| MCA[15:0]   | 16  | Main CPU address data bus           | 3.3V TTL  |

| MCFRAMEN MCBHEN MCBLEN MCRDYN MCDSN MCTREQN MCINTN                                   | 1<br>1<br>1<br>1<br>1<br>1                  | Main CPU #FRAME signal Main CPU #BHE signal Main CPU #BLE signal Main CPU #RDY signal Main CPU #DS signal Main CPU #TREQ signal Main CPU #INT signal                                                                       | 3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL                                     |

|--------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

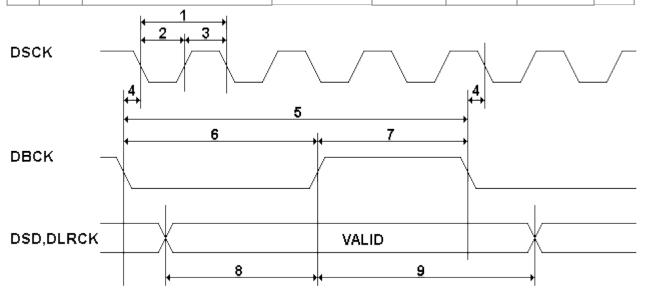

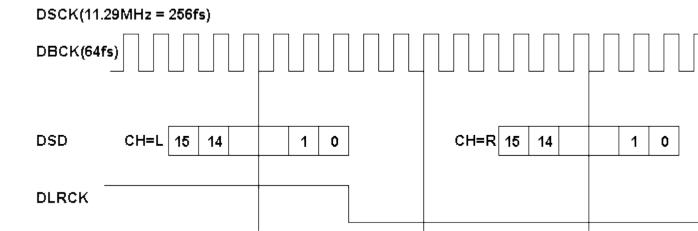

| DSD<br>DSCK<br>DBCK<br>DLRCK                                                         | 1<br>1<br>1                                 | DAC I/F serial data output DAC I/F system clock 256 fs DAC I/F BCK DAC I/F LRCK                                                                                                                                            | 3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL                                                             |

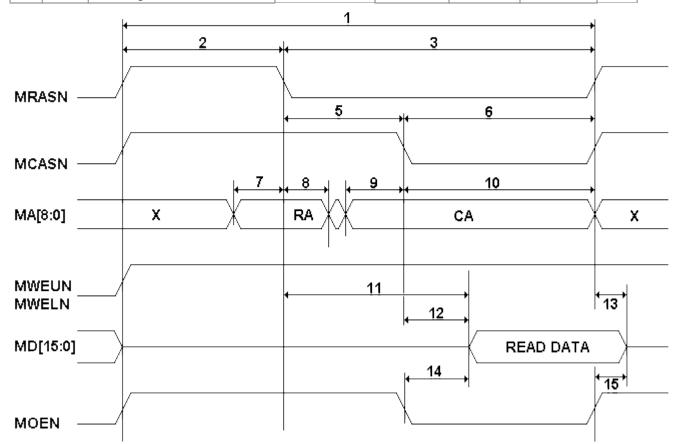

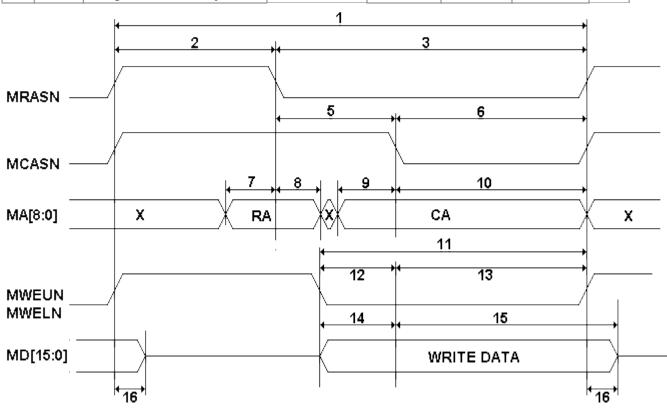

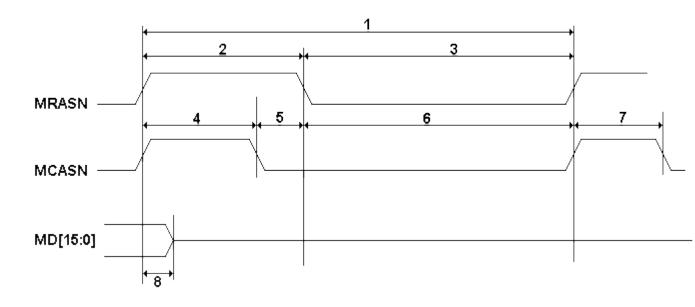

| MRASN[MWEN] MWEN[MCASLN] MCASN[MEASON] MCSN MCLK MLDQM MHDQM MHDQM MA[12:0] MD[15:0] | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>13<br>16 | Sound memory RAS signal Sound memory WE signal Sound memory CAS signal Sound memory CS signal CLK signal for sound memory LDQM signal for sound memory HDQM signal for sound memory Sound memory address Sound memory data | 3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL |

| VDD<br>VSS                                                                           | -<br> -                                     | Power source 3.3 V<br>GND                                                                                                                                                                                                  |                                                                                                          |

| NTRST<br>TCK<br>TDI<br>TDO<br>TMS                                                    | 1<br>1<br>1<br>1                            | Pins for embedded ICE                                                                                                                                                                                                      | 3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL<br>3.3V TTL                                                 |

| TEST[1:0]                                                                            | 2                                           | Pins for testing                                                                                                                                                                                                           |                                                                                                          |

| Total                                                                                | 85                                          | (128QFP)                                                                                                                                                                                                                   |                                                                                                          |

**Contents**

# **Block diagram**

# **Memory controller**

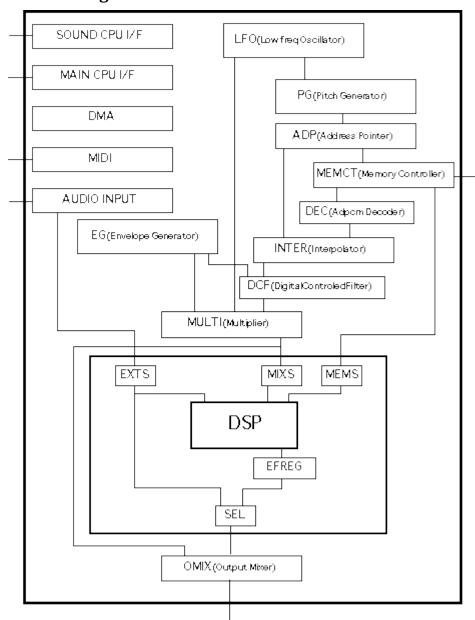

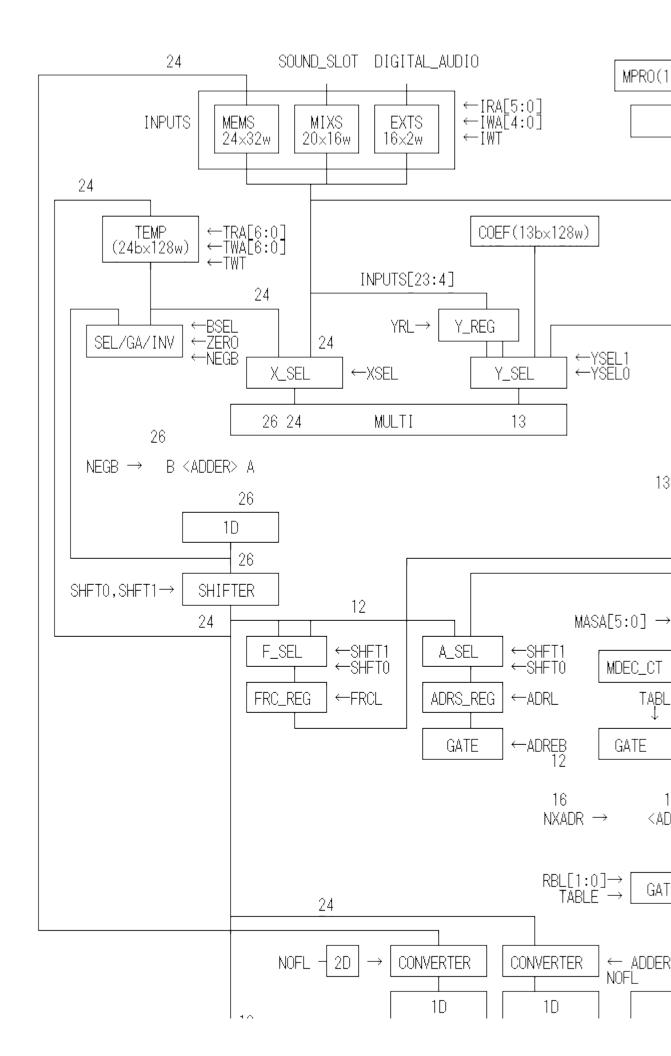

# Sound block diagram

DCF (Digital Controlled Filter)

**Contents**

# Register map

| ADDRESS           | AREA         |

|-------------------|--------------|

| 00000000~007FFFFF | DRAM_AREA*   |

| 00800000~008027FF | CHANNEL_DATA |

| 00802800~00802FFF | COMMON_DATA  |

| 00803000~00807FFF | DSP_DATA     |

#### Note:

Space that DRAM can use depends on on-board memory size.

# **Channel data**

Asterisks indicate changes after MIG.

| Asteris  | KS III                    | uica |       |             | 1                  | er wn  | G.    |       |             | -          |           |       |       |             | 1             |

|----------|---------------------------|------|-------|-------------|--------------------|--------|-------|-------|-------------|------------|-----------|-------|-------|-------------|---------------|

| ADDRESS  | 15                        | 14   | 13 13 | 2 11        | 10                 | 09     | 08    | 07    | 06 0        | )5         | 04        | 03    | 02    | 01 00       |               |

| 00800000 | KX                        | КВ   |       | -           | SS<br>*            | LP*    | PCM   | 1S*   |             |            | SA[2      | 22:16 | ]*    |             | KX:KYONE<br>X |

| 00800004 |                           |      |       |             |                    |        | SA[15 | 5:0]* | k           |            |           |       |       |             | LP:LPCTL      |

| 80000800 |                           |      |       |             |                    | I      | LSA[  | 15:0  | ]           |            |           |       |       |             | KB:KYONB      |

| 0080000C |                           |      |       |             |                    | Ι      | LEA[  | 15:0  | ]           |            |           |       |       |             | SS:SSCTL      |

| 00800010 | D2R[4:0] D1R[4:0] AR[4:0] |      |       |             |                    |        |       |       |             |            |           |       |       |             |               |

| 00800014 |                           | LS   | KR    | S[3:        | 0]                 |        | DL[   | 4:0]  |             |            |           | RR[4  | 4:0]  |             | LS:LPSLNK     |

| 00800018 |                           | OC   | T[3:  | 0]*         |                    |        |       |       | FN          | IS[        | 9:0]      |       |       |             |               |

| 0080001C | RE                        | I    | LFOF  | [4:0]       |                    | PLF    | OWS   |       | FOS <br>:0] | [2         | ALF       | OWS   | 1     | FOS[<br>:0] | RE:LFORE      |

| 00800020 |                           |      |       | T           | L[7                | :0]    |       |       | J           | SE         | EL[3:0    | 0]    |       |             |               |

| 00800024 | IN                        | 1XL  | [3:0] |             | DIS                | DL[3   | :0]   |       |             |            | Г         | IPAN  | v[4:0 | )]          |               |

| 00800028 |                           |      |       |             |                    | -      |       |       |             |            |           | Q[4:  | 0]*   |             |               |

| 0080002C |                           |      |       | FLV0[12:0]* |                    |        |       |       |             |            |           |       |       |             |               |

| 00800030 |                           |      |       |             |                    |        | F     | LV    | 1[12:       | :0]        | *         |       |       |             |               |

| 00800034 |                           |      |       |             |                    |        | F     | LV    | 2[12:       | :0]        | *         |       |       |             |               |

| 00800038 |                           |      |       |             | FLV3[12:0]*        |        |       |       |             |            |           |       |       |             |               |

| 0080003C |                           |      |       |             |                    |        | F     | LV    | 4[12:       | :0]        | *         |       |       |             |               |

| 00800040 |                           |      |       | I           | FAF                | R[4:0] |       |       |             |            | FD1R[4:0] |       |       |             |               |

| 00800044 |                           |      |       | F           | FD2R[4:0] FRR[4:0] |        |       |       |             |            |           |       |       |             |               |

| 00800080 |                           |      |       |             |                    |        |       |       |             |            |           |       |       |             |               |

| I        |                           |      |       | SL          | ОТ                 | 1 CO   | NTR   | OL    | REC         | SIS        | TER       |       |       |             |               |

| 008000C4 |                           |      |       |             |                    |        |       |       |             |            |           |       |       |             |               |

| 00801F80 |                           |      |       |             |                    |        |       |       |             |            |           |       |       |             |               |

| l        | SLOT 63 CONTROL REGISTER  |      |       |             |                    |        |       |       |             |            |           |       |       |             |               |

| 00801FC4 |                           |      |       |             |                    |        |       |       |             |            |           |       |       |             |               |

| 00802000 |                           |      |       |             | EFSDL[3:0]         |        |       |       |             | EFPAN[4:0] |           |       |       | )]          | DSP_OUT_1     |

| 00802044 |                           |      |       |             | EFS                | DL[3   | :0]   |       |             |            | E         | FPAN  | N[4:( | )]          | DSP_OUT_1     |

|          |                           |      |       |             |                    |        |       |       |             |            |           |       | -     | -           |               |

# Common data (not affected by channel)

Asterisks indicate changes after MIG.

| 1 10001101 | isterious indicate changes after 1411G. |               |    |    |                    |            |             |    |           |    |    |     |                      |                               |         |    |                   |

|------------|-----------------------------------------|---------------|----|----|--------------------|------------|-------------|----|-----------|----|----|-----|----------------------|-------------------------------|---------|----|-------------------|

| ADDRESS    | 15                                      | 14            | 13 | 12 | 11                 | 10         | 09          | 08 | 07        | 06 | 05 | 04  | 03                   | 02                            | 01      | 00 |                   |

| 00802800   | MN                                      | N M8 D8       |    | D8 | VER[3:0] MVOL[3:0] |            |             |    |           |    |    |     | D8:DAC18B M1:MEM8MB  |                               |         |    |                   |

| 00802804   | \$T                                     | RE            | 3L |    |                    |            | RBP[22:11]* |    |           |    |    |     | \$T:TESTB0 (IC TEST) |                               |         |    |                   |

| 00802808   |                                         |               |    | OF | OE                 | IO         | IF          |    |           |    | M  | IBU | F[7:                 | 0]                            |         |    | IF:MIFUL IO:MIOVF |

| 0080280C   |                                         | AF MSLC[5:0]* |    |    |                    | MOBUF[7:0] |             |    |           |    |    |     |                      | OE:MOEMP OF:MOFUL<br>AF:AFSET |         |    |                   |

| 00802810   | LP*                                     | SC            | GC |    |                    |            |             |    | EG[12:0]* |    |    |     |                      |                               | MN:Mono |    |                   |

| 00802814 |            |            | (           | CA[                | 15:0]* |       |           |       |                 |    |                         |                          |

|----------|------------|------------|-------------|--------------------|--------|-------|-----------|-------|-----------------|----|-------------------------|--------------------------|

| 00802880 |            | DMEA[22:16 | 5]          |                    | \$TSC  | D[2:0 | \$T       | MF    | \$*** (IC TEST) |    |                         |                          |

| 00802884 |            |            | DM          | EA[                | [15:1] |       |           |       |                 |    |                         |                          |

| 00802888 | GA         |            | DR          | GA                 | [14:1] |       |           |       |                 |    |                         |                          |

| 0080288C | DI         |            | DL          | .G[:               | 14:1]  |       |           |       |                 |    | EX                      | GA:DGATE DI:DDIR EX:DEXE |

| 00802890 |            |            | TACTI<br>0] | <b>.</b> [2:       |        | -     | ГΙМ.      | A[7:0 | 0]              |    |                         |                          |

| 00802894 |            |            | TBCTL 0]    | ـ[2:               |        | r     | ГΙМ       | B[7:0 | 0]              |    |                         |                          |

| 00802898 |            |            | TCCTL<br>0] | TCCTL[2: TIMC[7:0] |        |       |           |       |                 |    |                         |                          |

| 0080289C |            |            |             |                    | S      | CIEB  | [10:0     |       |                 |    |                         |                          |

| 008028A0 |            |            |             |                    | S      |       |           |       |                 |    |                         |                          |

| 008028A4 |            |            |             |                    | S      |       |           |       |                 |    |                         |                          |

| 008028A8 |            |            |             |                    |        |       |           |       |                 |    |                         |                          |

| 008028AC |            |            |             |                    |        | S     | CIL       |       |                 |    |                         |                          |

| 008028B0 |            |            |             |                    |        | S     | CIL       |       |                 |    |                         |                          |

| 008028B4 |            |            |             |                    | M      | CIEB  | [10:      | 0]    |                 |    |                         |                          |

| 008028B8 |            |            |             |                    | M      | CIPD  | [10:      | 0]    |                 |    |                         |                          |

| 008028BC |            |            |             |                    | M      | CIRE  | [10:      | 0]    |                 |    |                         |                          |

|          |            |            |             |                    |        |       |           |       |                 |    |                         |                          |

| 00802C00 |            |            |             |                    |        | AR    | AR:ARMRST |       |                 |    |                         |                          |

| 00802D00 |            |            |             | L7 L               | 6 L5   | L4    | L3        | L2    | L1              | L0 | 割り込み用 RP:ReadProtection |                          |

| 00802D04 |            |            |             | RP                 | M7 M   | [6 M5 | M4        | M3    | M2              | M1 | M0                      | 割り込み用                    |

| 00802E00 |            |            | R           | ΓC[                | 31:16] | *     |           |       |                 |    |                         |                          |

| 00802E04 | RTC[15:0]* |            |             |                    |        |       |           |       |                 |    |                         |                          |

# **DSP** data

Asterisks indicate changes after MIG.

| Asterisks indicate changes after MIG. |                               |                                  |     |     |      |      |     |     |     |        |                 |     |              |       |        |    |        |

|---------------------------------------|-------------------------------|----------------------------------|-----|-----|------|------|-----|-----|-----|--------|-----------------|-----|--------------|-------|--------|----|--------|

| ADDRESS                               | 15                            | 14                               | 13  | 12  | 11   | 10   | 09  | 80  | 07  | 06     | 05              | 04  | 03           | 02    | 01     | 00 |        |

| 00803000                              |                               |                                  |     |     |      |      |     |     |     |        |                 |     |              |       |        |    |        |

| I                                     |                               | COEF REG "COEF[12:0]" 00 00 00   |     |     |      |      |     |     |     |        |                 |     |              | 00    | 00~127 |    |        |

| 008031FF                              |                               |                                  |     |     |      |      |     |     |     |        |                 |     |              |       |        |    |        |

| 00803200                              |                               |                                  |     |     |      |      |     |     |     |        |                 |     |              |       |        |    |        |

| I                                     |                               | MEMORY ADDRESS REG "MADRS[16:1]" |     |     |      |      |     |     |     |        |                 |     |              | 00~63 |        |    |        |

| 008032FF                              |                               |                                  |     |     |      |      |     |     |     |        |                 |     |              |       |        |    |        |

| 00803400                              |                               |                                  | DS1 | P M | ICF  | RO I | PRO | OGF | RAN | /I ''I | ИPF             | RO[ | 63:4         | 48]'  | 1      |    |        |

| 00803404                              |                               |                                  | DS  | P M | IICI | ROI  | PRC | )GR | RAN | 1 ''N  | /IPF            | O[4 | <b>47:</b> 3 | 32]"  |        |    | CTED 0 |

| 00803408                              |                               |                                  | DS  | P M | IICI | ROI  | PRC | OGR | RAN | 1 ''N  | 1PF             | O[  | 31:1         | [6]   |        |    | STEP_0 |

| 0080340C                              | DSP MICROPROGRAM "MPRO[15:0]" |                                  |     |     |      |      |     |     |     |        |                 |     |              |       |        |    |        |

| 00803410                              |                               |                                  |     |     |      |      |     |     |     |        | STEP_1~STEP_126 |     |              |       |        |    |        |

| 00803BEC             |                   |                                     |             |          |  |  |  |  |  |  |

|----------------------|-------------------|-------------------------------------|-------------|----------|--|--|--|--|--|--|

| 00803BF0             | DSP MICRO PROGE   |                                     |             |          |  |  |  |  |  |  |

| 00803BF4             | DSP MICROPROGR    |                                     |             |          |  |  |  |  |  |  |

| 00803BF8             | DSP MICROPROGR    | RAM "MPRO[3                         | 31:16]"     | STEP_127 |  |  |  |  |  |  |

| 00803BFC             | DSP MICROPROGI    | RAM "MPRO[                          | 15:0]"      |          |  |  |  |  |  |  |

| 00804000             |                   | LOW "TE                             | MP[7:0]"    |          |  |  |  |  |  |  |

|                      | TEMPBUFFER H      | TEMPBUFFER HIGH "TEMP[23:8]"        |             |          |  |  |  |  |  |  |

| 008043FF             |                   | LOW "MI                             |             |          |  |  |  |  |  |  |

| 00804400             |                   |                                     |             |          |  |  |  |  |  |  |

|                      | SOUND MEMORY DAT  | SOUND MEMORY DATA HIGH "MEMS[23:8]" |             |          |  |  |  |  |  |  |

| 008044FF             |                   |                                     |             |          |  |  |  |  |  |  |

| 00804500             |                   |                                     | "MIXS[3:0]" |          |  |  |  |  |  |  |

| 00004575             | MIXSOUND SLOT DAT | TA STACK "M                         | IXS[19:4]"  | 00~15    |  |  |  |  |  |  |

| 0080457F<br>00804580 |                   |                                     |             |          |  |  |  |  |  |  |

| 00004360             | EFCTED DATA OUT   | ГРUТ "EFREC                         | G[15:0]"    | 00~15    |  |  |  |  |  |  |

| 008045BF             |                   |                                     |             |          |  |  |  |  |  |  |

| 008045C0             | EXTERNAL INPUT D  | OATA STACK                          | "EXTS"      | 00~01    |  |  |  |  |  |  |

| 008045C7             |                   |                                     |             |          |  |  |  |  |  |  |

|                      |                   |                                     |             | 8.       |  |  |  |  |  |  |

**Contents**

# **Overview of Registers**

### **Channel data**

#### **KYONEX**

All slots are made KEY\_ON or OFF when "1" is written. Writing"0" has no effect.

#### **KYONB**

Registers KEY\_ON or OFF.

(To simultaneously make KEY\_ON, set this bit to "1" for all slots to be made ON, and write "1" to KEYONEX of any of those slots.

#### **SSCTL**

- 0: Uses local SDRAM data as sound input data.

- 1: Uses noise as sound input data.

#### **LPCTL**

- 0: Loop OFF

(LSA and LEA settings are necessary, so processing ends when LEA is reached.)

- 1: Forward loop

#### **PCMS[1:0]**

- 0: 16-bit PCM (2's complement format)

- 1: 8-bit PCM (2's complement format)

- 2: 4-bit ADPCM (Yamaha format)

- 3: Use prohibited

#### **SA [22:0]**

Start address of sound data specified with byte address.

However, when PCMS = 0, SA0 (LSB of SA [22:0]) has to be "0". @

#### LSA [15:0]

Loop start address of sound data specified with sample count from SA(Start Address).

- 1: Sample frequency is byte count for PCM8B = 1, word (16-bit) count for PCM8B = 0, and 1/2 byte count for ADPCM.

- 2: Minimum value that can be set is restricted by the pitch and loop mode.

#### **LEA [15:0]**

Loop end address of sound data specified with sample count from SA.

- 1: Maximum value that can be set is restricted by the pitch and loop mode.

- 2: To enable interpolation, setting of LEA = FFFF[X] is prohibited.

- 3: SA \* LSA regardless of loop mode.

Notes on loop

#### AR [4:0]

Specifies the rate of transition of EG in attack status. (Volume transition is increased.)

#### **DIR [4:0]**

Specifies the rate of transition of EG in decay 1 status. (Volume transition is decreased.)

#### D2R [4:0]

Specifies the rate of transition of EG in decay 2 status. (Volume transition is decreased.)

#### **RR** [4:0]

Specifies the rate of transition of EG in release status. (Volume transition is decreased.)

#### DL [4:0]

Specify the EG level for the transition from decay 1 to decay 2.

#### KRS [3:0]

Specifies the rate of the EG key rate scaling. (Integer)

#### **LPSLNK**

Loop start link function: EG shifts to decay 1 when the address of the read sound\_slot\_input\_data exceeds the loop start address.

(When EG = "000", there is no transition.) For this case, there may not be a transition to decay 2, depending on the setting of DL register.

#### Notes on EG

#### **OCT** [3:0]

Specifies octave as two's complement.

Values in parentheses are +1 octave for ADPCM.

| ОСТ  | 8  | 9  | A  | В  | C  | D  | E  | F  | 0 | 1  | 2    | 3    | 4    | 5    | 6    | 7    |

|------|----|----|----|----|----|----|----|----|---|----|------|------|------|------|------|------|

| Tone | -8 | -7 | -6 | -5 | -4 | -3 | -2 | -1 | 0 | +1 | (+2) | (+3) | (+4) | (+5) | (+6) | (+7) |

#### FNS [9:0]

Specifies sound pitch setting to FNS and OCT register.

#### Pitch: P [CENT] = $1200 \times LOG 2 ((210 + FNS)/210)$

For FNS = 0 (and OCT = 0), the tone matches the sampling source.

Also, the pitch difference (pitch precision) equivalent to the LSB of FNS is 1.69 centimeters.

#### Notes on PG

#### **LFORE**

Specifies whether or not to initialize LFO.

(Setting has no effect if noise has been selected.)

- 1: Resets LFO.

- 0: Does not reset LFO.

#### **LFOF [4:0]**

Specifies the oscillation frequency of LFO.

(Setting has no effect if noise has been selected.)

#### **ALFOWS [1: 0]**

Specifies the shape of the ALFO waveform.

#### **PLFOWS** [1: 0]

Specifies the shape of the PLFO waveform.

#### **ALFOS [2:0]**

Specifies the extent of mixing to the EG of LFO.

#### **PLFOS [2:0]**

Specifies the extent of the effect on the pitch of LFO.

#### Notes on LFO

#### **ISEL** [3:0]

Specifies the mix register address for each slot when sound slot output data is input to the DSP's mix register (MIXS).

#### Note:

MIXS is the input for DSP to obtain the sum of the input for all slots.

- MIXS has an area for adding per slot, and an area for keeping the interval of one sample; these areas can be allocated alternately. Hence, reading by the DSP side can be done at any step.

- Input to MIXS must be set so that the sum does not overflow 0 dB. (There is no overflow protect function.)

#### TL [7:0]

Total level: The actual amount of attenuation is specified by placing this value in the EG value.

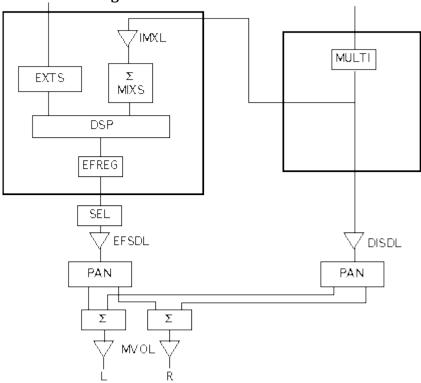

#### **DIPAN [4:0]**

Specifies the position for each slot when direct data is sent.

#### **EFPAN [4:0]**

Specifies the position for each slot for effect data and external input data.

#### IMXL [3:0]

Specifies the level for each slot when sound slot output data is input to the DSP mix register (MIXS).

#### **DISDL** [3:0]

Specifies the send level for each slot when direct data is output to DAC.

### **EFSDL** [3:0]

Specifies the send level when effect data and external input data is sent to DAC. The send level is specified for each slot. (Codes are the same as for DISDL.)

| Register | Volume |

|----------|--------|

| 0        | -MAXdB |

| 1        | -42dB  |

| 2        | -39dB  |

|          |        |

| D        | -6dB   |

| E        | -3dB   |

| F        | 0dB    |

Notes on mixer

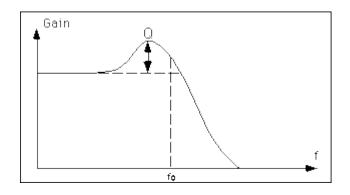

#### Q [4:0]

Resonance data

Sets Q for the FEG filter. Values from -3.00 through 20.25 dB can be set. The relationships between bits and gain are as follows:

#### $Q [dB] = 0.75 \times register value -3$

Example of setting

| Lampi | e or sett.   | <del></del> |              |

|-------|--------------|-------------|--------------|

| DATA  | GAIN[<br>dB] | DATA        | GAIN[<br>dB] |

| 11111 | 20.25        | 00100       | 0.00         |

| 11100 | 18.00        | 00011       | -0.75        |

| 11000 | 15.00        | 00010       | -1.50        |

| 10000 | 9.00         | 00001       | -2.25        |

| 01100 | 6.00         | 00000       | -3.00        |

| 01000 | 3.00         |             |              |

| 00110 | 1.50         |             |              |

|       |              |             |              |

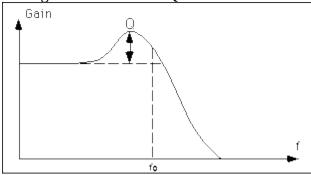

The following figure defines Q.

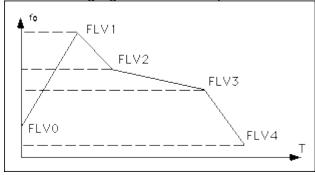

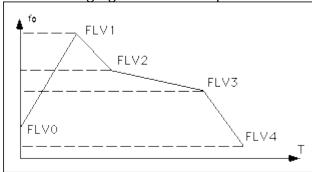

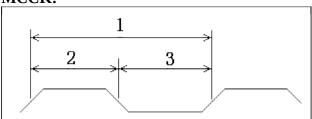

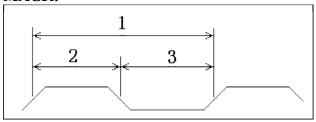

#### FLV0 [12:0]

Cutoff frequency at the time of attack start

#### FLV1 [12:0]

Cutoff frequency at the time of attack end (dacay start time)

#### FLV2 [12:0]

Cutoff frequency at the time of decay end (sustain start time)

#### FLV3 [12:0]

Cutoff frequency at the time of KOFF

#### FLV4 [12:0]

Cutoff frequency after release

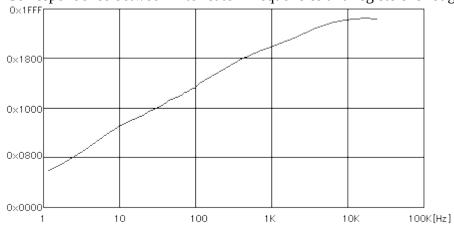

The following figure shows the operation of the registers.

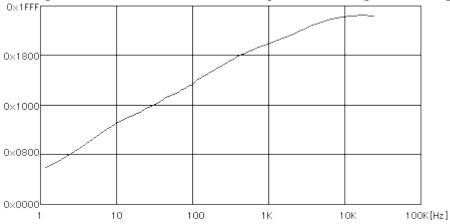

Correspondence between filter cutoff frequencies and registers is roughly as below.

\* When filter is through, Q is 4H and FLV\* is 1FFFH.

Specifies the rate of transition of FEG in attack status. (Volume transition is increased.)

#### FD1R [4:0]

Specifies the rate of transition of FEG in decay 1 status. (Volume transition is decreased.)

#### FD2R [4:0]

Specifies the rate of transition of FEG in decay 2 status. (Volume transition is decreased.)

#### FRR [4:0]

Specifies the rate of transition of FEG in release status. (Volume transition is decreased.)

#### Common data

#### **MONO**

- 1: Makes panpot?? information invalid.

- 0: Makes panpot information valid.

#### Note:

When panpot information has been made invalid, the sound coming from the channel on one side will double in volume, so the setting of MVOL must be lowered.

#### MVOL [3:0]

Master volume for digital output to DAC

#### Mixer notes

#### DAC18B

- 1: The digital output is the 18-bit DAC interface.

- 0: The digital output is the 16-bit DAC interface.

#### **MEM8MB**

Specifies the memory to be used.

- 0: 16M\_DRAM

- 1: 64M DRAM

Relationships between sound memory space and used memory

#### **VER [3:0]**

Reads out the LSI version based on this manual.

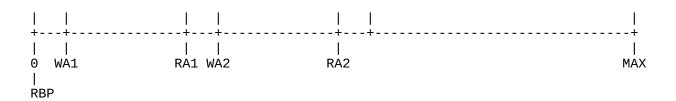

#### **RBL** [1:0]

Specifies the length of the ring buffer.

- 0: 8 K words

- 1: 16 K words

- 2: 32 K words

- 3: 64 K words

#### **RBP** [22:11]

Specifies the leading address of the ring buffer. (1 K word limit)

#### **MIBUF [7:0]**

MIDI input data buffer. (Consists of four-byte FIFO.)

#### **MIOVF**

Indicates that the input FIFO has overflowed.

#### **MIFUL**

Indicates that the input FIFO is full.

(The above two flags show the status before MIBUF [7:0] is read.)

#### **MOFUL**

Indicates that the output FIFO is full.

#### **MOEMP**

Indicates that the output FIFO is empty.

#### **MOBUF [7:0]**

MIDI output data buffer

#### **AFSEL**

Decides whether to make the EG monitor AEG or FEG.

- 0: AEG monitor

- 1: FEG monitor

#### MSLC [5:0]

Specifies the slot number to monitor SGC, CA, EG, and LP.

#### SGC [1:0]

Monitors the status of the current EG.

- 0: Attack

- 1: Decay 1

- 2: Decay 2

- 3: Release

#### **CA** [15:10]

Currently, shows the sample position read from the sound source as the 16 high-order bits of the relative sample No. from SA. The lowest order bit is equivalent to one sample.

#### EG [12:0]

Monitors the 13 high-order bits of the current EG value. During AEG monitoring, the low-order three bits are always "0".

#### LP

Loop end flag

The channel is selected by MSLC [5:0]. This flag shows that the loop has ended.

This flag is cleared to "0" when it is read.

#### **MRWINH [3:0]**

Writing "1" to this flag prohibits reading for the corresponding sound memory access. (Register access cannot be prohibited.)

- Bit 0: Access by DSP

- Bit 1: Read by sound source

- Bit 2: Access by SCPU (Reading by SCPU prohibited because cancel cannot be done from SCPU.)

- Bit 3: Access by MCPU

#### **DGATE**

Specifies to clear the DMA transmission destination field to "0".

- 0: Does not clear to "0".

- 1: Clears to "0".

#### **DDIR**

Specifies the direction for DMA transmission.

- 0: Transmits from sound memory to SCSP register.

- 1: Transmits from SCSP register to sound memory.

#### **DEXE**

Specifies the start of DMA. (Cleared to "0" when DMA ends.)

- DMA starts when "1" is written.

- Writing "0" has no effect.

#### **DMEA** [22:1]

The word address specifies the sound memory address that starts DMA.

#### **DRGA** [14:1]

The word address specifies the internal register address that starts DMA.

#### **DLG** [14:1]

Specifies the DMA transmission word count.

#### **Caution:**

Fields of the source and destination must not exceed the memory fields or internal register fields. During DMA transmission, registers associated with DMA must not be changed.

#### **Notes:**

Registers are assigned to the memory 100000-100EE3.

The transmission address always changes in the increasing direction.

### **TACTL [2:0]**

Specifies the increment cycle of timer A.

- 0: One increment per sample.

- 1: One increment per two samples.

- 2: One increment per four samples.

- 3: One increment per eight samples.

- 4: One increment per 16 samples.

- 5: One increment per 32 samples.

- 6: One increment per 64 samples.

- 7: One increment per 128 samples.

#### **TIMA [7:0]**

Timer A (Generates an interrupt request at the timing when the UP counter changes from all "1" to all "0".)

#### **TBCTL [2:0]**

Specifies the increment cycle for timer B. (The code is the same as for timer A.)

#### TIMB [7:0]

Timer B (Generation of interrupt is the same as for timer A.)

#### **TCCTL [2:0]**

Specifies the increment cycle for timer C. (The code is the same as for timer A.)

#### **TIMC [7:0]**

Timer C (Generation of interrupt is the same as for timer A.)

### **SCIPD** [10:0]

Holds the SCPU interrupt request. (Bit correspondence is as below.)

- Bit 0 (R): Requests interrupt to external interrupt input pin "INTON". (SCSI)

- Bit 1 (R): Reserved.

- Bit 2 (R): Reserved.

- Bit 3 (R): MIDI input interrupt.

(Interrupt request generated when input FIFO has fetched valid data. Hence, if the CPU reads FIFO data, it must read the lot once and leave the FIFO empty. When the FIFO has

- changed to empty status, the interrupt request is canceled automatically.)

Bit 4 (R): DMA end interrupt

- Bit 5 (R/W): SCPU interrupt caused by data being written to the CPU, so only "1" can be written. (Writing "0" has no effect.) This flag can be set from either the MCPU or the SCPU.

- Bit 6 (R): Timer A interrupt

- Bit 7 (R): Timer B interrupt

- Bit 8 (R): Timer C interrupt

- Bit 9 (R): MIDI output interrupt.

(If the output FIFO changes to empty status, an interrupt request is generated.)

(If the status is no longer empty because data is written to the output FIFO, the interrupt request is canceled automatically.)

- Bit 10 (R): Interrupt of one sample interval

#### **SCIEB** [10:0]

Permits an interrupt for the bit corresponding to "1" for the SCPU interrupt permission register.

#### **SCIRE [10:0]**

Resets the interrupt request corresponding to the bit written with "1".

#### **SCILV0 [7:0]**

Specifies bit 0 of the SCPU interrupt level code defined by the bit correspondence.

#### **SCILV1** [7:0]

Specifies bit 1 of the SCPU interrupt level code defined by the bit correspondence.

#### **SCILV2** [7:0]

Specifies bit 2 of the SCPU interrupt level code defined by the bit correspondence. (See SCIPD for bit correspondence.)

#### **Notes:**

Bit 7 can be used to make one specification for the level of the interrupt request bits 7, 8, 9, and 10.

For the interrupt level by INTON, SCILV2 [0], SCILV1 [0], and SCILV0 [0] correspond to pins SCIPL2N, SCIPL1N, AND SCIPL0N.

#### MCIPD [10:0]

Holds the MCPU interrupt request.

- Bit 0 (R): Interrupt to external interrupt input pin "INTON". (SCSI)

- Bit 1 (R): Reserved.

- Bit 2 (R): Reserved.

- Bit 3 (R): MIDI input interrupt.

(Interrupt request generated when input FIFO has fetched valid data. Hence, if the CPU reads FIFO data, it must read the lot once and leave the FIFO empty. When the FIFO has changed to empty status, the interrupt request is canceled automatically.)

- Bit 4 (R): DMA end interrupt

- Bit 5 (R/W): MCPU interrupt caused by data being written to the CPU, so only "1" can be written. (Writing "0" has no effect.)

This flag can be set from either the MCPU or the SCPU.

- Bit 6 (R): Timer A interrupt

- Bit 7 (R): Timer B interrupt

- Bit 8 (R): Timer C interrupt

- Bit 9 (R): MIDI output interrupt.

(If the output FIFO changes to empty status, an interrupt request is generated.)

(If the status is no longer empty because data is written to the output FIFO, the interrupt request is canceled automatically.)

- Bit 10 (R): Interrupt of one sample interval

#### MCIEB [10:0]

Permits an interrupt for the bit corresponding to "1" for the MCPU interrupt permission register.

#### MCIRE [10:0]

Resets the interrupt request corresponding to the bit written with "1".

#### Note:

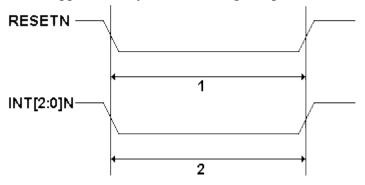

When the above interrupt request starts, the MCPU interrupt signal MCINTN generates a negative pulse corresponding to one clock of MCCK.

The interrupt level cannot be specified for the MCPU interrupt.

#### **ARMRST**

Resets ARM7DI.

- 0: Reset.

- 1: Reset canceled.

#### Note:

This register can be controlled from the main CPU only.

#### RP

Sets the DRAM control from the main CPU to the read only status for reading DRAM data.

- 0: Main CPU can read and write DRAM.

- 1: Main CPU can read DRAM.

#### Note:

This register can perform control from the ARM7DI side only.

#### L [7:0]

Indicates the No. of the interrupt arriving at ARM7DI. Here, L [7:3] must be used.

#### Note:

This register can perform control from the ARM7DI side only.

#### M [7:0]

Sets this bit to "1" when ARM7DI completes interrupt processing, so as to notify interrupt end to the AICA sound block. Here, M [7:1] must be used.

#### Note:

This register can perform control from the ARM7DI side only.

#### RTC [31:0] (R/W)

Indicates the status of the counter that increments by 1 every second. Can count approximately 136 years with 32 bits.

#### **DSP** data

#### **COEF** [12:0]

Buffer for the DSP data quantity. (Data quantity: 128)

#### **Caution:**

If the conventional data width of 16 bits is expanded, write "0" to the three undefined lower-order bits of the register map so as to maintain compatibility.

#### **MADRS** [16:1]

Buffer for DSP addresses. (Data quantity: 64)

#### MPRO [63:0]

Buffer for DSP microprograms. (Data quantity: 128)

#### **TEMP [23:0]**

DSP work buffer. (Data quantity: 128)

Configured as a ring buffer. The pointer decrements by 1 for each sample.

#### **MEMS [23:0]**

Input-data-buffer from wave-memory (Data quantity: 32)

The actual write to MEMS [7:0] is executed at the same time as the write to MEMS [23:16].

#### MIXS [19:0]

Buffer for sound data from input mixer. (Data quantity: 16)

#### Caution:

Writing to MIXS [19:0] is used for LSI tests. Writing other than in test mode is invalid for the following reasons:

- Regardless of the setting, data is constantly being written from the sound block.

- A second generation's worth of data is held for adding all slots, but the generation cannot be specified at access.

#### **EFREG [15:0]**

DSP output buffer. (Data quantity: 16)

#### **EXTS [15:0]**

Data buffer for digital audio input. (Data quantity: 4)

# **Overview of Technology**

### **Loop Control**

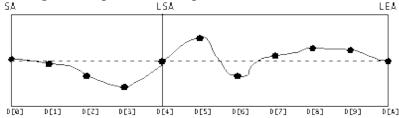

Settings for loop data and loop-associated addresses are as below.

Settings for the above data are "3" for LSA and "A" for LEA.

Further, when SA is 100h, the sound memory is allocated as below. (Little-endian)

| When PCMS = 2 (ADPCM) |       |      |     |     |  |  |  |  |

|-----------------------|-------|------|-----|-----|--|--|--|--|

|                       | 15-12 | 15-8 | 7-4 | 3-0 |  |  |  |  |

| 100                   | D3    | D2   | D1  | D0  |  |  |  |  |

| 102                   | D7    | D6   | D5  | D4  |  |  |  |  |

| 104                   |       | DA   | D9  | D8  |  |  |  |  |

|                       |       |      |     |     |  |  |  |  |

| When PCMS = 1         |       |      |     |     |  |  |  |  |

| When PCMS = 0 |      |  |  |  |  |

|---------------|------|--|--|--|--|

|               | 15-0 |  |  |  |  |

| 100           | D0   |  |  |  |  |

| 102           | D1   |  |  |  |  |

|               | :    |  |  |  |  |

| 112           | D9   |  |  |  |  |

| 114           | DA   |  |  |  |  |

|               |      |  |  |  |  |

| When PCMS = 1 |      |     |  |  |  |  |

|---------------|------|-----|--|--|--|--|

|               | 15-8 | 7-0 |  |  |  |  |

| 100           | D1   | D0  |  |  |  |  |

| 102           | D3   | D2  |  |  |  |  |

|               | :    |     |  |  |  |  |

| 108           | D9   | D8  |  |  |  |  |

| 10A           |      | DA  |  |  |  |  |

Additionally, the readout order in each loop mode is as follows, assuming that sound data is read for each sample.

Loop OFF

$$D0\rightarrow D1\rightarrow D2\rightarrow \cdot \cdot \cdot \rightarrow DA$$

Loop ON

Notes on loop processing

- Loop processing is premised on data corresponding to LSA and LEA (for ADPCM, data after decoding) having the same value. Hence, (for ADPCM, data after encoding), if necessary, make the settings so they have the same value (data prior to encoding).

- If the pitch is raised for short loop data (waveform data having few extremes that corresponds to the loop--data from LSA through LEA), it is possible that data corresponding to the loop section may not be read out at all. In this case, loop processing cannot be done correctly. To enable processing, the values will have to be set so that LEA-LSA >= OCT (with code) 2, in view of the effect of pitch such as FNS and PLFO.

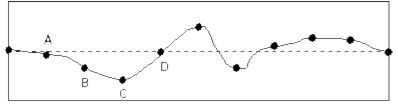

#### **ADPCM**

This LSI uses the Adaptive Differential Pulse Code Modulation (ADPCM) format for the sound data compression function. ADPCM is a data compression format that prevents sound quality from deteriorating by codifying, based on a quantized width adapted flexibly to changes in the waveform created from the difference between the sound data and the predicted data.

### Method of Encoding

This LSI turns four-bit ADPCM data into 16-bit PCM data. Encoding is done by the procedure below.

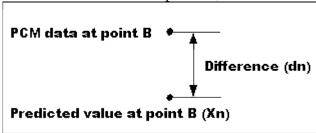

1. Data to be encoded is converted to 16-bit PCM data each sampling cycle.

2. PCM data at point B and the predicted value (Xn) at point B are compared, and the difference (dn) found. At this time, the MSB (L4) of the ADPCM data is set to "0" if the value of the difference is positive, and to "1" if negative.

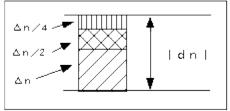

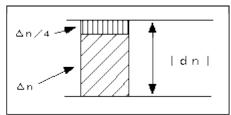

3. Next, the quantized width ( $\Delta n$ ) and the absolute value of the difference (|dn|) are compared, and the remaining three ADPCM data bits (L3, L2, L1) for point B are decided from the ADPCM data correspondence table in Table 1.

### • Example 1

When the difference | dn | is the quantized width  $(\Delta n) * 7/4$ , as in Fig. a, the remaining three bits of ADPCM data become L3 = 1, L2 = 1, L1 = 1.

### • Example 2

When the difference | dn | is the quantized width ( $\Delta$ n) \* 5/4, as in Fig. b, the remaining three bits of ADPCM data become L3 = 1, L2 = 0, L1 = 1.

Fig. a

Fig. b

- 4. When the ADPCM data for point B is obtained, the ADPCM data for point C is found by getting the predicted value for point C (Xn + 1) and the quantized width for point C ( $\Delta$  = 1).

- The predicted value for point C (Xn + 1) = (1 2 \* L4) \* (L3 + L2/2 + L1/4 + 1/8) \* quantized width  $(\Delta n)$  + predicted value (Xn) for point B.

- The quantized width  $(\Delta n + 1) = f(L3, L2, L1) *$  quantized width  $(\Delta n) f(L3, L2, L1)$  is the rate of change in the quantized width found from <u>Table 2</u>. Further, the initial value of the predicted value is zero; the initial value of the quantized width is 127, its minimum value is 127, and its maximum value is 24576.

ADPCM encoding data is obtained by repeating the above procedure.

Table 1:ADPCM data correspondence table

| Tubic 1.2 | able 1:11D1 Civi data correspondence table |    |    |     |                                                       |  |  |  |

|-----------|--------------------------------------------|----|----|-----|-------------------------------------------------------|--|--|--|

| L         | 4                                          | L3 | L2 | I.1 | 条件                                                    |  |  |  |

| dn≧0      | dn≦0                                       | LS | LZ | L1  | 宗<br>                                                 |  |  |  |

|           |                                            | 0  | 0  | 0   | d n   <△n ∕ 4                                         |  |  |  |

|           |                                            | 0  | 0  | 1   | $\triangle n / 4 \le  d n  < \triangle n / 2$         |  |  |  |

|           |                                            | 0  | 1  | 0   | $\triangle n / 2 \le  d n  < \triangle n * 3 / 4$     |  |  |  |

| 0         | 1                                          | 0  | 1  | 1   | $\triangle n * 3 / 4 \le   d n   < \triangle n$       |  |  |  |

| 0         | 1                                          | 1  | 0  | 0   | $\triangle n \leq  d n  < \triangle n * 5 / 4$        |  |  |  |

|           |                                            | 1  | 0  | 1   | $\Delta n * 5 / 4 \leq   d n   < \Delta n * 3 / 2$    |  |  |  |

|           |                                            | 1  | 1  | 0   | $\triangle n * 3 / 2 \le  d n  < \triangle n * 7 / 4$ |  |  |  |

|           |                                            | 1  | 1  | 1   | $\triangle n * 7 / 4 \le   d n  $                     |  |  |  |

Table 2:Rate of transition in quantized width

| L3 | L2 | L1 | f          |

|----|----|----|------------|

| 0  | 0  | 0  | 0.8984375  |

| 0  | 0  | 1  | 0.8984375  |

| 0  | 1  | 0  | 0.8984375  |

| 0  | 1  | 1  | 0.8984375  |

| 1  | 0  | 0  | 1.19921875 |

| 1  | 0  | 1  | 1.59765625 |

| 1  | 1  | 0  | 2.0        |

| 1  | 1  | 1  | 2.3984375  |

# **Method of Decoding**

The decoding method is found in the same way as the predicted value and quantized width are found for encoding. The procedure is as below.

1. The decode value (Xn) at point B is found from the four-bit ADPCM data, quantized width ( $\Delta$ n), and decode value (Xn - 1) at point A.

ADPCM DATA

The decode value (Xn) at point B = (1 - 2 \* L4) \* (L3 + L2/2 + L1/4 + 1/8) \* quantized width ( $\Delta$ n) + decode value (Xn - 1) at point A.

2. Next, to find the decode value (Xn + 1) at point C, the quantized width  $(\Delta n + 1)$  is updated.

The quantized width  $(\Delta n + 1) = f(L3, L2, L1) * quantized width <math>(\Delta n)$ .

Decoding is done by repeating the above procedure.

#### **AEG**

AEG transition rate change by the key scalling value. Execution rate is found from the following equation, and the real transition time is found from the transition time corresponding to the excution rate value on the time.

Execution rate and AEG transition time

Execution rate = (KRS[3:0]+OCT[3:0] \* 2 + FNS[9] + rate [register setting value]) \* 2 There are each register value within the bounds of following.

```

KRS[3:0]:+0 ~ +F[H]

OCT[3:0]:-8 ~ +7[H]

FNS[9] :+0 , +1[H]

rate[register setting value]):+0 ~ +1F[H]

```

|                | Attack Status                         |                |                                    |  |  |  |  |  |

|----------------|---------------------------------------|----------------|------------------------------------|--|--|--|--|--|

| Effective rate | Transition<br>time[ms]<br>[-96dB~0dB] | Effective rate | Transition time[ms]<br>[-96dB~0dB] |  |  |  |  |  |

| 0              | infinity                              | 32             | 47.0                               |  |  |  |  |  |

| 1              | infinity                              | 33             | 38.0                               |  |  |  |  |  |

| 2              | 8100.0                                | 34             | 31.0                               |  |  |  |  |  |

| 3              | 6900.0                                | 35             | 27.0                               |  |  |  |  |  |

| 4              | 6000.0                                | 36             | 24.0                               |  |  |  |  |  |

| 5              | 4800.0                                | 37             | 19.0                               |  |  |  |  |  |

| 6              | 4000.0                                | 38             | 15.0                               |  |  |  |  |  |

| 7              | 3400.0                                | 39             | 13.0                               |  |  |  |  |  |

| 8              | 3000.0                                | 40             | 12.0                               |  |  |  |  |  |

| 9              | 2400.0                                | 41             | 9.4                                |  |  |  |  |  |

| 10             | 2000.0                                | 42             | 7.9                                |  |  |  |  |  |

| 11             | 1700.0                                | 43             | 6.8                                |  |  |  |  |  |

| 12             | 1500.0                                | 44             | 6.0                                |  |  |  |  |  |

| 13             | 1200.0                                | 45             | 4.7                                |  |  |  |  |  |

| 14             | 1000.0                                | 46             | 3.8                                |  |  |  |  |  |

| 15             | 860.0                                 | 47             | 3.4                                |  |  |  |  |  |

| 16             | 760.0                                 | 48             | 3.0                                |  |  |  |  |  |

| 17             | 600.0                                 | 49             | 2.4                                |  |  |  |  |  |

| 18             | 500.0                                 | 50             | 2.0                                |  |  |  |  |  |

| Effective rate                   | Transition time[ms] | Effective rate | Transition time[ms] |  |  |  |  |

|----------------------------------|---------------------|----------------|---------------------|--|--|--|--|

| Decay 1, Decay 2, Release Status |                     |                |                     |  |  |  |  |

| 31                               | 55.0                | 63             | 0.0                 |  |  |  |  |

| 30                               | 63.0                | 62             | 0.0                 |  |  |  |  |

| 29                               | 76.0                | 61             | 0.35                |  |  |  |  |

| 28                               | 95.0                | 60             | 0.40                |  |  |  |  |

| 27                               | 110.0               | 59             | 0.44                |  |  |  |  |

| 26                               | 130.0               | 58             | 0.53                |  |  |  |  |

| 25                               | 150.0               | 57             | 0.65                |  |  |  |  |

| 24                               | 190.0               | 56             | 0.85                |  |  |  |  |

| 23                               | 220.0               | 55             | 0.93                |  |  |  |  |

| 22                               | 250.0               | 54             | 1.1                 |  |  |  |  |

| 21                               | 300.0               | 53             | 1.3                 |  |  |  |  |

| 20                               | 380.0               | 52             | 1.6                 |  |  |  |  |

| 19                               | 430.0               | 51             | 1.8                 |  |  |  |  |

| Effective rate | Transition<br>time[ms]<br>[0dB~-96dB] | Effective rate | Transition time[ms] [0dB~-96dB] |

|----------------|---------------------------------------|----------------|---------------------------------|

| 0              | infinity                              | 32             | 690.0                           |

| 1              | infinity                              | 33             | 550.0                           |

| 2              | 118200.0                              | 34             | 460.0                           |

| 3              | 101300.0                              | 35             | 390.0                           |

| 4              | 88600.0                               | 36             | 340.0                           |

| 5              | 70900.0                               | 37             | 270.0                           |

| 6              | 59100.0                               | 38             | 230.0                           |

| 7              | 50700.0                               | 39             | 200.0                           |

| 8              | 44300.0                               | 40             | 170.0                           |

| 9              | 35500.0                               | 41             | 140.0                           |

| 10             | 29600.0                               | 42             | 110.0                           |

| 11             | 25300.0                               | 43             | 98.0                            |

| 12             | 22200.0                               | 44             | 85.0                            |

| 13             | 17700.0                               | 45             | 68.0                            |

| 14             | 14800.0                               | 46             | 57.0                            |

| 15             | 12700.0                               | 47             | 49.0                            |

| 16             | 11100.0                               | 48             | 43.0                            |

| 17             | 8900.0                                | 49             | 34.0                            |

| 18             | 7400.0                                | 50             | 28.0                            |

| 19             | 6300.0                                | 51             | 25.0                            |

| 20             | 5500.0                                | 52             | 22.0                            |

| 21             | 4400.0                                | 53             | 18.0                            |

| 22             | 3700.0                                | 54             | 14.0                            |

| 23             | 3200.0                                | 55             | 12.0                            |

| 24             | 2800.0                                | 56             | 11.0                            |

| 25             | 2200.0                                | 57             | 8.5                             |

| 26 | 1800.0 | 58 | 7.1 |

|----|--------|----|-----|

| 27 | 1600.0 | 59 | 6.1 |

| 28 | 1400.0 | 60 | 5.4 |

| 29 | 1100.0 | 61 | 4.3 |

| 30 | 920.0  | 62 | 3.6 |

| 31 | 790.0  | 63 | 3.1 |

### PG

# • Settings for OCT [3:0]

Specifies octave as two's complement. Values in parentheses are +1 octave for ADPCM.

| OCT  |    |    |    |    |    |    |    |    |   |    |      |      |      |      |      |      |

|------|----|----|----|----|----|----|----|----|---|----|------|------|------|------|------|------|

| Tone | -8 | -7 | -6 | -5 | -4 | -3 | -2 | -1 | 0 | +1 | (+2) | (+3) | (+4) | (+5) | (+6) | (+7) |

• Settings for FNS and OCT (The example gives settings for the F number table when the C4 note has been sampled at 44.1 KHz.)

Putting the above in a different form, FNS[DEC] = 210 \* (2P / 1200 - 1)

| Note | Note No. | Pitch<br>P[CENT] | FNS[9:0]<br>[DEC] | FNS[9:0]<br>[X] | OCT[3:0]<br>[X] |

|------|----------|------------------|-------------------|-----------------|-----------------|

| В3   | 59       | -100             | 909.1             | 38D             | F               |

| C4   | 60       | 0                | 0.0               | 0               | 0               |

| C4#  | 61       | 100              | 60.9              | 3D              | 0               |

| D4   | 62       | 200              | 125.4             | 7D              | 0               |

| D4#  | 63       | 300              | 193.7             | C2              | 0               |

| E4   | 64       | 400              | 266.2             | 10A             | Θ               |

| F4   | 65       | 500              | 342.9             | 157             | Θ               |

| F4#  | 66       | 600              | 424.2             | 1A8             | Θ               |

| G4   | 67       | 700              | 510.3             | 1FE             | Θ               |

| G4#  | 68       | 800              | 601.5             | 25A             | Θ               |

| A4   | 69       | 900              | 698.2             | 2BA             | Θ               |

| A4#  | 70       | 1000             | 800.6             | 321             | 0               |

| В4   | 71       | 1100             | 909.1             | 38D             | 0               |

| C5   | 72       | 0                | 0.0               | 0               | 1               |

### **LFO**

• Frequencies generated by LFOF [4:0]

| LFO[4:0] | frequencie<br>[Hz] | LFO[4:0] | frequencie<br>[Hz] |

|----------|--------------------|----------|--------------------|

| 00       | 0.17               | 10       | 2.87               |

| 01       | 0.19               | 11       | 3.31               |

| 02       | 0.23               | 12       | 3.92               |

| 03       | 0.27               | 13       | 4.79               |

| 04       | 0.34               | 14       | 6.15               |

| 05       | 0.39               | 15       | 7.18               |

| 06       | 0.45               | 16       | 8.60               |

| 07         | 0.55 | 17 | 10.80  |

|------------|------|----|--------|

| 80         | 0.68 | 18 | 14.40  |

| 09         | 0.78 | 19 | 17.20  |

| 0A         | 0.92 | 1A | 21.50  |

| 0B         | 1.10 | 1B | 28.70  |

| 0C         | 1.39 | 1C | 43.10  |

| 0D         | 1.60 | 1D | 57.40  |

| <b>0</b> E | 1.87 | 1E | 86.10  |

| 0F         | 2.27 | 1F | 172.30 |

- Form of ALFO wave by ALFOWS [1:0]

Form of PLFO wave by PLFOWS [1:0]

| ALFOWS | AM modulation (ALFO) |           |             |  |  |  |

|--------|----------------------|-----------|-------------|--|--|--|

| [X]    | Volume               | ALFO[7:0] | ALFO wave   |  |  |  |

|        | -0dB                 | 00        | \ \         |  |  |  |

|        | :                    | :         |             |  |  |  |

| 0      | :                    | :         |             |  |  |  |

|        | :                    | :         |             |  |  |  |

|        | :                    | FF        | <u> </u>    |  |  |  |

|        | -0dB                 | 00        |             |  |  |  |

|        | :                    | :         |             |  |  |  |

| 1      | :                    | :         |             |  |  |  |

|        | :                    | :         |             |  |  |  |

|        | :                    | FF        |             |  |  |  |

|        | -0dB                 | 00        |             |  |  |  |

|        | :                    | :         |             |  |  |  |

| 2      | :                    | :         |             |  |  |  |

|        | •                    | :         |             |  |  |  |

|        | :                    | FF        |             |  |  |  |

|        | -0dB                 | 00        | :*****      |  |  |  |

| 3      | :                    | :         | *****       |  |  |  |

|        | :                    | :         | ** Noise ** |  |  |  |

|        | :                    | :         | *****       |  |  |  |

|        | :                    | FF        | :++++++++++ |  |  |  |

| <b>PLFOWS</b> | P     | on (PLFO) |           |  |  |

|---------------|-------|-----------|-----------|--|--|

| [X]           | Pitch | PLFO[7:0] | PLFO wave |  |  |

|               | +     | 7F        | 1         |  |  |

|               | :     | :         |           |  |  |

| 0             | 0     | 00        |           |  |  |

|               | :     | :         |           |  |  |

|               | -     | 80        | V         |  |  |

|               | +     | 7F        |           |  |  |

|               | :     | :         |           |  |  |

| 1             | 0     | 00        |           |  |  |

|               | :     | :         |           |  |  |

|               | -     | 80        |           |  |  |

| 2 | +<br>:<br>0<br>: | 7F<br>:<br>00<br>:<br>80 |                                        |

|---|------------------|--------------------------|----------------------------------------|

| 3 | +<br>:<br>0<br>: | 7F<br>:<br>00<br>:<br>80 | ************************************** |

- Extent of mixing by ALFOS [2:0]Extent of effect on pitch by PLFOS [2:0]

| ALFO[X] | Mixing for EG        |

|---------|----------------------|

| 0       | No effect            |

| 1       | 4dB displacement     |

| 2       | 8dB displacement     |

| 3       | -1.5dB displacement  |

| 4       | -3.0dB displacement  |

| 5       | -6.0dB displacement  |

| 6       | -12.0dB displacement |

| 7       | -24.0dB displacement |

| PLFO[X] | Effect on pitch |     |   |   |     |       |              |

|---------|-----------------|-----|---|---|-----|-------|--------------|

| 0       |                 |     |   |   | No  | effec | t            |

| 1       | -               | 3   | ~ | + | 2   | CENT  | displacement |

| 2       | -               | 7   | ~ | + | 5   | CENT  | displacement |

| 3       | -               | 14  | ~ | + | 12  | CENT  | displacement |

| 4       | -               | 27  | ~ | + | 25  | CENT  | displacement |

| 5       | -               | 55  | ~ | + | 52  | CENT  | displacement |

| 6       | -               | 112 | ~ | + | 103 | CENT  | displacement |

| 7       | -               | 231 | ~ | + | 202 | CENT  | displacement |

# Mixer

# • Volume and registers

# TL[7:0]

|        | bit7  | bit6  | bit5  | bit4 | bit3 | bit2   | bit1   | bit0   |

|--------|-------|-------|-------|------|------|--------|--------|--------|

| Volume | -48dB | -24dB | -12dB | -6dB | -3dB | -1.5dB | -0.8dB | -0.4dB |

# IMXL[3:0],DISDL[3:0],EFSDL[3:0],MVOL[3:0]

| Register | Volume  |

|----------|---------|

| 0        | -MAX dB |

| 1        | -42 dB  |

| 2        | -39 dB  |

| :        | :       |

| D        | -6 dB   |

| E | -3 dB |

|---|-------|

| F | 0 dB  |

# **DIPAN[4:0],EFPAN[4:0]**

| Register            | $oxed{L}$        |                | R             |                |

|---------------------|------------------|----------------|---------------|----------------|

| 0                   | 0                | dB             | 0             | dB             |

| 1                   | -3               | dB             | 0             | dB             |

| 2                   | -6               | dB             | 0             | dB             |

| :                   | :                |                | :             |                |

| D                   | -39              | dB             | 0             | dB             |

| E                   | -42              | dB             | 0             | dB             |

| F                   | -MAX             | dB             | Θ             | dB             |

|                     |                  |                |               |                |

| Register            | L                | ı              | R             |                |

| Register<br>10      | <b>L</b>         | dB             | <b>R</b> 0    | dB             |

|                     | 0                |                | 0             |                |

| 10                  | 0                | dB             | -3            | dB             |

| 10<br>11            | 0                | dB<br>dB       | -3            | dB<br>dB       |

| 10<br>11            | 0<br>0<br>0      | dB<br>dB       | 0<br>-3<br>-6 | dB<br>dB<br>dB |

| 10<br>11<br>12<br>: | 0<br>0<br>0<br>: | dB<br>dB<br>dB | 0<br>-3<br>-6 | dB<br>dB<br>dB |

• Correspondence between effect sources and slots that EFSDL and EFPAN should set

| Slot | Output mixer source data |

|------|--------------------------|

| 0F   | EFREG[0]EFREG[15]        |

| 10   | Digital audio 1L         |

| 11   | Digital audio 1R         |

# Mixer block diagram

#### **FEG**

The IIR filter enables LPF to pass through each channel.

The dedicated EG enables time variance of the LPG cutoff frequency.

LPF supports fixed (no time variance) Q (resonance) setting for each channel.

#### **Q** [12:0]Resonance data

Sets Q for the FEG filter. Setting can be done from 0 through 48 dB. The relationships between bits and gain are as below.

| DATA       | GAIN[dB] |

|------------|----------|

| Q12        | 48.0     |

| Q11        | 24.0     |

| Q10        | 12.0     |

| Q9         | 6.0      |

| Q8         | 3.0      |

| <b>Q</b> 7 | 1.5      |

| Q6         | 0.75     |

| <b>Q</b> 5 | 0.375    |

| Q4         | 0.375/ 2 |

| Q3         | 0.375/ 4 |

| Q2         | 0.375/ 8 |

| Q1         | 0.375/16 |

| Q0         | 0.375/32 |

The figure below defines Q.

#### **FAR [4:0]**

Specifies the rate of the FEG transition in attack status.

#### FD1R [4:0]

Specifies the rate of the FEG transition in decay 1 status.

#### FD2R [4:0]

Specifies the rate of the FEG transition in decay 2 status.

#### FRR [4:0]

Specifies the rate of the FEG transition in release status.

The rate and transition time for each register is the same as for AEG.

#### FLV0 [12:0]

Cutoff frequency at attack start

#### FLV1 [12:0]

Cutoff frequency at attack end (when decay starts)

#### FLV2 [12:0]

Cutoff frequency at decay end (when sustain starts)

#### FLV3 [12:0]

Cutoff frequency at KOFF

#### FLV4 [12:0]

Cutoff frequency after release

The following figure shows the operation of the registers.

Correspondence between filter cutoff frequencies and registers is roughly as below.

#### **FAR [4:0]**

Specifies the rate of transition of FEG in attack status. (Volume transition is increased.)

#### FD1R [4:0]

Specifies the rate of transition of FEG in decay 1 status. (Volume transition is decreased.)

#### FD2R [4:0]

Specifies the rate of transition of FEG in decay 2 status. (Volume transition is decreased.)

#### FRR [4:0]

Specifies the rate of transition of FEG in release status. (Volume transition is decreased.)

#### **Execution rate and FEG transition time**

\_\_\_\_\_\_

| Effective rate | Transition time<br>[ms] | Effective rate | Transition time [ms] |

|----------------|-------------------------|----------------|----------------------|

| 0              | infinity                | 32             | 690.0                |

| 1              | infinity                | 33             | 550.0                |

| 2              | 118200.0                | 34             | 460.0                |

| 3              | 101300.0                | 35             | 390.0                |

| 4              | 88600.0                 | 36             | 340.0                |

| 5              | 70900.0                 | 37             | 270.0                |

| 6              | 59100.0                 | 38             | 230.0                |

| 7              | 50700.0                 | 39             | 200.0                |

| 8              | 44300.0                 | 40             | 170.0                |

| 9              | 35500.0                 | 41             | 140.0                |

| 10             | 29600.0                 | 42             | 110.0                |

| 11             | 25300.0                 | 43             | 98.0                 |

| 12             | 22200.0                 | 44             | 85.0                 |

| 13             | 17700.0                 | 45             | 68.0                 |

| 14             | 14800.0                 | 46             | 57.0                 |

| 15             | 12700.0                 | 47             | 49.0                 |

| 16             | 11100.0                 | 48             | 43.0                 |

| 17             | 8900.0                  | 49             | 34.0                 |

| 18             | 7400.0                  | 50             | 28.0                 |

| 19             | 6300.0                  | 51             | 25.0                 |

| 20             | 5500.0                  | 52             | 22.0                 |

| 21             | 4400.0                  | 53             | 18.0                 |

| 22             | 3700.0                  | 54             | 14.0                 |

| 23             | 3200.0                  | 55             | 12.0                 |

| 24             | 2800.0                  | 56             | 11.0                 |

| 25             | 2200.0                  | 57             | 8.5                  |

| 26             | 1800.0                  | 58             | 7.1                  |

| 27             | 1600.0                  | 59             | 6.1                  |

| 28             | 1400.0                  | 60             | 5.4                  |

| 29             | 1100.0                  | 61             | 4.3                  |

| 30             | 920.0                   | 62             | 3.6                  |

| 31             | 790.0                   | 63             | 3.1                  |

#### **RBL** [1:0] (W):

Specifies length of ring buffer.

| RBL[1:0]ring buffer |    |        |

|---------------------|----|--------|

| 0                   | 8  | Kwords |

| 1                   | 16 | Kwords |

| 2                   | 32 | Kwords |

| 3                   | 64 | Kwords |

#### **RBP** [22:11] (W):

Specifies leading address of ring buffer. (4 Kword limit)

#### Generates modulation waveform used with DSP